Data sheet acquired from Harris Semiconductor SCHS031B – Revised July 2003

# CD4026B, CD4033B Types

## CMOS **Decade Counters/Dividers**

High-Voltage Types (20-Volt Rating) With Decoded 7-Segment Display Outputs and: Display Enable - CD4026B Ripple Blanking — CD4033B

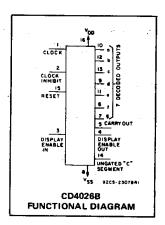

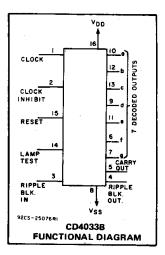

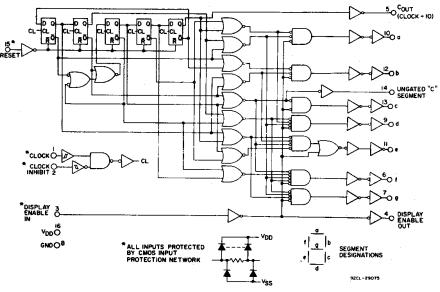

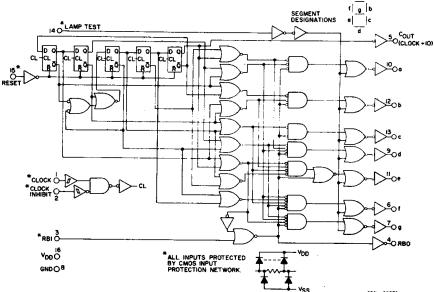

■ CD4026B and CD4033B each consist of a 5-stage Johnson decade counter and an output decoder which converts the Johnson code to a 7-segment decoded output for driving one stage in a numerical display.

These devices are particularly advantageous in display applications where low power dissipation and/or low package count are important.

Inputs common to both types are CLOCK, RESET, & CLOCK INHIBIT; common outputs are CARRY OUT and the seven decoded outputs (a, b, c, d, e, f, g). tional inputs and outputs for the CD4026B include DISPLAY ENABLE input and DISPLAY ENABLE and UNGATED "C-SEGMENT" outputs. Signals peculiar to the CD4033B are RIPPLE-BLANKING INPUT AND LAMP TEST INPUT and a RIPPLE-BLANKING OUTPUT.

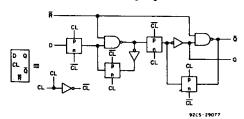

A high RESET signal clears the decade counter to its zero count. The counter is advanced one count at the positive clock signal transition if the CLOCK INHIBIT signal is low. Counter advancement via the clock line is inhibited when the CLOCK INHIBIT signal is high. The CLOCK INHI-BIT signal can be used as a negative-edge clock if the clock line is held high. Antilock gating is provided on the JOHNSON counter, thus assuring proper counting sequence. The CARRY-OUT (Cout) signal completes one cycle every ten CLOCK INPUT cycles and is used to clock the succeeding decade directly in a multi-decade counting chain. The seven decoded outputs (a, b, c, d, e, f, g) illuminate the proper segments in a seven

- Counter and 7-segment decoding in one package

- Easily interfaced with 7-segment display types

- Fully static counter operation: DC to 6 MHz (typ.) at VDD=10 V

- Ideal for low-power displays

- Display enable output (CD4026B)

- "Ripple blanking" and lamp test (CD4033B)

- 100% tested for quiescent current at 20 V

- Standardized, symmetrical output characteristics

- 5-V, 10-V, and 15-V parametric ratings

- Schmitt-triggered clock inputs

- Meets all requirements of JEDEC Tentative Standard No. 13B, "Standard Specifications for Description of 'B' Series CMOS Devices" **Applications**

- Decade counting 7-segment decimal display

- Frequency division 7-segment decimal displays

- Clocks, watches, timers (e.g. ÷60, ÷ 60, ÷ 12 counter/display)

- Counter/display driver for meter applications

segment display device used for representing when the DISPLAY ENABLE IN is high.

# the decimal numbers 0 to 9. The 7-segment outputs go high on selection in the CD4033B; in the CD4026B these outputs go high only

### MAXIMUM RATINGS, Absolute-Maximum Values: DC SUPPLY-VOLTAGE RANGE, (VDD) Voltages referenced to VSS Terminal) ..... -0.5V to +20V INPUT VOLTAGE RANGE, ALL INPUTS .....-0.5V to V<sub>DD</sub> +0.5V DC INPUT CURRENT, ANY ONE INPUT ...... ±10mA POWER DISSIPATION PER PACKAGE (PD): For T<sub>A</sub> = +100°C to +125°C...... Derate Linearity at 12mW/°C to 200mW **DEVICE DISSIPATION PER OUTPUT TRANSISTOR** OPERATING-TEMPERATURE RANGE (T<sub>A</sub>).....-55°C to +125°C STORAGE TEMPERATURE RANGE (T<sub>stg</sub>).....-65°C to +150°C LEAD TEMPERATURE (DURING SOLDERING):

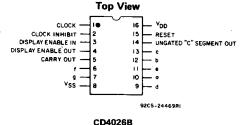

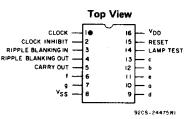

## **TERMINAL DIAGRAMS**

CD4033B

#### **RECOMMENDED OPERATING CONDITIONS**

For maximum reliability, nominal operating conditions should be selected so that operation is always within the following ranges:

| CHARACTERISTIC                                    |                                         | V <sub>DD</sub> | ι                | UNITS           |     |  |

|---------------------------------------------------|-----------------------------------------|-----------------|------------------|-----------------|-----|--|

| A CONTRACTOR                                      | <u> </u>                                | (V)             | MIN.             | MAX.            | ]   |  |

| Supply-Voltage Range (For T<br>Temperature Range) | A = Full Package                        |                 | 3                | 18              | V   |  |

| Clock Input Frequency,                            | <sup>f</sup> CL                         | 5<br>10<br>15   | -<br>-           | 2.5<br>5.5<br>8 | MHz |  |

| Clock Pulse Width,                                | tWCL .                                  | 5<br>10<br>15   | 220<br>100<br>80 | -<br>-<br>-     |     |  |

| Clock Rise and Fall Time,                         | <b><sup>†</sup>CL</b> , <sup>‡</sup> CL | 5<br>10<br>15   | -                | Unlimited       | :   |  |

| Clock Inhibit Set Up Time,                        | <sup>t</sup> SU                         | 5<br>10<br>15   | 200<br>50<br>30  |                 | ns  |  |

| Reset Pulse Width,                                | t <sub>W</sub>                          | 5<br>10<br>15   | 200<br>100<br>50 | -<br>-<br>-     |     |  |

| Reset Removal Time                                |                                         | 5<br>10<br>15   | 30<br>15<br>10   |                 |     |  |

#### STATIC ELECTRICAL CHARACTERISTICS

| CHARACTER-                                                                                  | CONDITIONS |      |     | LIMITS AT INDICATED TEMPERATURES (°C) |            |       |       |       |                   | UNITS          |       |  |

|---------------------------------------------------------------------------------------------|------------|------|-----|---------------------------------------|------------|-------|-------|-------|-------------------|----------------|-------|--|

| ISTIC                                                                                       | Vo         | VIN  |     | +25                                   |            |       |       |       |                   |                | UNITS |  |

|                                                                                             | (V)        | (V)  |     | -55                                   | <b>-40</b> | +85   | +125  | Min.  | Тур.              | Max.           |       |  |

| Quiescent Device<br>Current,<br>IDD Max.                                                    | -          | 0,5  | 5   | 5                                     | 5          | 150   | 150   | _     | 0.04              | 5              | μΑ    |  |

|                                                                                             | -          | 0,10 | 10  | 10                                    | 10         | 300   | 300   | _     | 0.04              | 10             |       |  |

|                                                                                             | -          | 0,15 | 15  | 20                                    | 20         | 600   | 600   | _     | 0.04              | 20             |       |  |

|                                                                                             | _          | 0,20 | 20  | 100                                   | 100        | 3000  | 3000  | _     | 0.08              | 100            |       |  |

| Output Low<br>(Sink) Current<br>IOL Min.<br>Output High<br>(Source)<br>Current,<br>IOH Min. | 0.4        | 0,5  | - 5 | 0.64                                  | 0.61       | 0.42  | 0.36  | 0.51  | 1                 | -              |       |  |

|                                                                                             | 0.5        | 0,10 | 10  | 1.6                                   | 1.5        | 1.1   | 0.9   | 1.3   | 2.6               | -              |       |  |

|                                                                                             | 1.5        | 0,15 | 15  | 4.2                                   | 4          | 2.8   | 2.4   | 3.4   | 6.8               | _              |       |  |

|                                                                                             | 4.6        | 0,5  | 5   | -0.64                                 | -0.61      | -0.42 | -0.36 | -0.51 | -1                |                | mA    |  |

|                                                                                             | 2,5        | 0,5  | 5   | -2                                    | -1.8       | -1.3  | -1.15 | -1.6  | -3.2              | 1              |       |  |

|                                                                                             | 9.5        | 0,10 | 10  | -1.6                                  | -1.5       | -1.1  | -0.9  | -1.3  | -2.6              | : -            |       |  |

|                                                                                             | 13.5       | 0,15 | 15  | -4.2                                  | _4         | -2.8  | -2.4  | -3.4  | -6.8              | 1              |       |  |

| Output Voltage:<br>Low-Level,<br>VOL Max.                                                   | -          | 0,5  | 5   | 0.05                                  |            |       |       | -     | 0                 | 0.05           | >     |  |

|                                                                                             | -          | 0,10 | 10  | 0.05                                  |            |       |       | -     | - 0               | 0.05           |       |  |

|                                                                                             | _          | 0,15 | 15  | 0.05                                  |            |       | . =   | 0     | 0.05              |                |       |  |

| Output Voltage:                                                                             | -          | 0,5  | 5   | 4.95 4.95 5                           |            |       |       | +     | ]                 |                |       |  |

| High Level,                                                                                 | -          | 0,10 | 10  | 9.95                                  |            |       |       | 9.95  | 10                | 1              |       |  |

| VOH Min.                                                                                    | _          | 0,15 | 15  |                                       | 14         | .95   |       | 14.95 | 15                | +              |       |  |

| Input Low<br>Voltage,<br>VIL Max.                                                           | 0.5, 4.5   | _    | 5   |                                       | 1          | .5    |       | - ·   | -                 | 1.5            |       |  |

|                                                                                             | 1, 9       | -    | 10  |                                       |            | 3     |       |       | -                 | 3              |       |  |

|                                                                                             | 1.5,13.5   |      | 15  | 4                                     |            |       | 1     | _     | 4                 | ] <sub>v</sub> |       |  |

| Input High<br>Voltage,<br>VIH Min.                                                          | 0.5, 4.5   | -    | 5   | 3.5                                   |            |       | 3.5   |       | -                 | v              |       |  |

|                                                                                             | 1, 9       |      | 10  | 7                                     |            |       | 7     | -     |                   |                |       |  |

|                                                                                             | 1.5,13.5   | ,    | 15  | 11                                    |            |       |       | 11    |                   |                |       |  |

| Input Current                                                                               | -          | 0,18 | 18  | ±0.1                                  | ±0.1       | ±1    | ±1    |       | ±10 <sup>-5</sup> | ±0.1           | μΑ    |  |

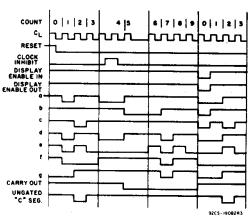

#### CD4026B

When the DISPLAY ENABLE IN is low the seven decoded outputs are forced low regardless of the state of the counter. Activation of the display only when required results in significant power savings. This system also facilitates implementation of display-character multiplexing.

The CARRY OUT and UNGATED "C-SEGMENT" signals are not gated by the DISPLAY ENABLE and therefore are available continuously. This feature is a requirement in implementation of certain divider functions such as divide-by-60 and divide-by-12.

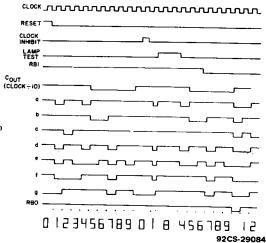

#### CD4033B

The CD4033B has provisions for automatic blanking of the non-significant zeros in a multi-digit decimal number which results in an easily readable display consistent with normal writing practice. For example, the number 0050.0700 in an eight digit display would be displayed as 50.07. Zero suppression on the integer side is obtained by connecting the RBI terminal of the CD4033B associated with the most significant digit in the display to a low-level voltage and connecting the RBO terminal of that stage to the RBI terminal of the CD4033B in the next-lower significant position in the display. This procedure is continued for each succeeding CD4033B on the integer side of the display.

On the fraction side of the display the RBI of the CD4033B associated with the least significant bit is connected to a low-level voltage and the RBO of that CD4033B is connected to the RBI terminal of the CD4033B in the next more-significant-bit position. Again, this procedure is continued for all CD4033B's on the fraction side of the display.

In a purely fractional number the zero immediately preceding the decimal point can be displayed by connecting the RBI of that stage to a high level voltage (instead of to the RBO of the next more-significant-stage). For example: optional zero → 0.7346. Likewise, the zero in a number such as 763.0 can be displayed by connecting the RBI of the CD4033B associated with it to a high-level voltage.

Ripple blanking of non-significant zeros provides an appreciable savings in display power.

The CD4033B has a LAMP TEST input which, when connected to a high-level voltage, overrides normal decoder operation and enables a check to be made on possible display malfunctions by putting the seven outputs in the high state.

The CD4026B- and CD4033B-series types are supplied in 16-lead dual-in-line plastic packages (E suffix), 16-lead small-outline packages (NSR suffix), and 16-lead thin shrink small-outline packages (PW and PWR suffixes).

Fig. 1 - CD4026B logic diagram.

Fig. 2 - CD4033B logic diagram.

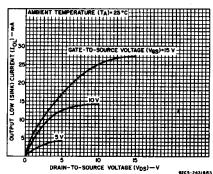

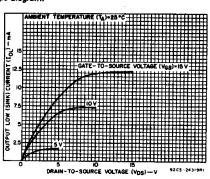

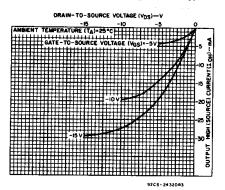

Fig. 6 — Typical n-channel output low (sink) current characteristics.

Fig. 7 - Minimum n-channel output low (sink) current characteristics.

Fig. 3 — CD4026B timing diagram.

Fig. 4 -- CD4033B timing diagram.

Fig. 5 — Detail of typical flip-flop stage for both types.

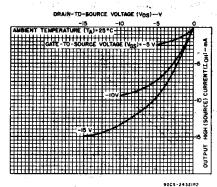

Fig. 8 — Typical p-channel output high (source) current characteristics.

# DYNAMIC ELECTRICAL CHARACTERISTICS at $T_A$ = 25°C, Input $t_r$ , $t_f$ = 20 ns, $C_L$ = 60 pF, $R_L$ = 200 k $\Omega$

|                                                     |                                          | TEST<br>CONDITIONS | LIMITS                 |           |      |      |       |

|-----------------------------------------------------|------------------------------------------|--------------------|------------------------|-----------|------|------|-------|

| CHARACTERISTIC                                      | en e |                    | V <sub>DD</sub><br>(V) | Min.      | Тур. | Max. | UNITS |

| CLOCKED OPERATION                                   |                                          |                    |                        | 4.5       |      |      | -     |

| Propagation Delay Time;                             | t <sub>PLH</sub> , t <sub>PHL</sub>      |                    | 5                      |           | 250  | 500  |       |

| Carry-Out Line                                      |                                          |                    | 10                     |           | 100  | 200  | 1     |

| <u></u>                                             |                                          | 1                  | 15                     | _         | 75   | 150  |       |

|                                                     |                                          |                    | 5                      | _         | 350  | 700  |       |

| Decode Outlines                                     |                                          |                    | 10                     | _         | 125  | 250  | ns    |

|                                                     |                                          |                    | 15                     | _         | 90   | 180  | '     |

| Transition Time;                                    | tTHL, tTLH                               |                    | 5                      | _         | 100  | 200  |       |

| Carry-Out Line                                      |                                          |                    | 10                     |           | 50   | 100  |       |

|                                                     |                                          | 1                  | 15                     | _         | 25   | 50   |       |

| Maximum Clock Input Free                            | quency, f <sub>CL</sub> ▲                |                    | 5                      | 2.5       | 5    | _    |       |

| er er gelden er |                                          |                    | 10                     | 5.5       | 11   | _    | MHz   |

|                                                     |                                          |                    | 15                     | 8         | 16   | _    |       |

| Min. Clock Pulse Width,                             | t <sub>W</sub> .                         | :                  | 5                      | _         | 110  | 220  |       |

|                                                     | **                                       |                    | 10                     | _         | 50   | 100  |       |

|                                                     |                                          |                    | 15                     | _         | 40   | 80   |       |

| Clock and Clock Inhibit Rise or Fall Time;          |                                          |                    | 5                      |           |      |      |       |

|                                                     | <sup>t</sup> rCL <sup>, t</sup> fCL      |                    | 10                     | Unlimited |      | d    | ns    |

|                                                     |                                          |                    | 15                     | <u> </u>  |      |      |       |

| Average Input Capacitance, C <sub>IN</sub>          |                                          | Any Input          | Any Input              |           |      | 7    | pF    |

| RESET OPERATION                                     |                                          |                    |                        |           |      |      |       |

| Propagation Delay Time;                             |                                          |                    | 5                      |           | 275  | 550  |       |

| To Carry-Out Line,                                  | <sup>t</sup> PLH                         |                    | 10                     |           | _    | 240  |       |

|                                                     |                                          | }                  | 15                     |           |      | 160  |       |

| To Decode Out Lines,                                | tPHL, tPLH                               |                    | 5                      |           |      | 600  |       |

| ,                                                   | COL TLA                                  |                    | 10                     | _         |      | 250  |       |

|                                                     |                                          | ]                  | 15                     | -         | _    | 180  |       |

| Min. Reset Pulse Width,                             | tw                                       |                    | 5                      | _         |      | 120  | ns .  |

| * .                                                 | •                                        | 121                | 10                     |           |      | 100  |       |

| <u> </u>                                            | and the first section of                 | 1.2                | 15                     | _         | 25   | 50   |       |

| Min. Reset Removal Time                             |                                          | **                 | 5                      | _         | 0    | 30   |       |

|                                                     | " " " " " " " " " " " " " " " " " " "    |                    | 10                     | _         | 0    | 15   |       |

|                                                     | *                                        |                    | 15                     |           | 0    | 10   |       |

<sup>▲</sup> Measured with respect to carry-out line.

Fig. 9 – Minimum p-channel output high (source) current characteristics.

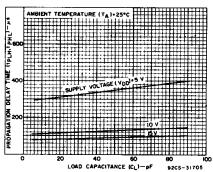

Fig. 10 — Typical propagation delay time as a function of load capacitance for decoded outputs.

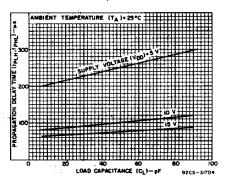

Fig. 11 — Typical propagation delay time as a function of load capacitance for carry-out outputs.

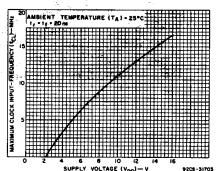

Fig. 12 - Typical maximum clock input-frequency as a function of supply voltage.

Dimensions in parentheses are in millimeters and are derived from the basic inch dimensions as indicated. Grid graduations are in mils (10<sup>-3</sup> inch).

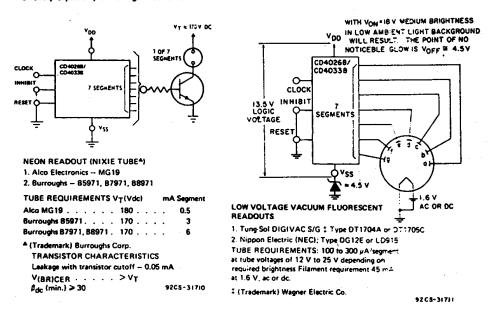

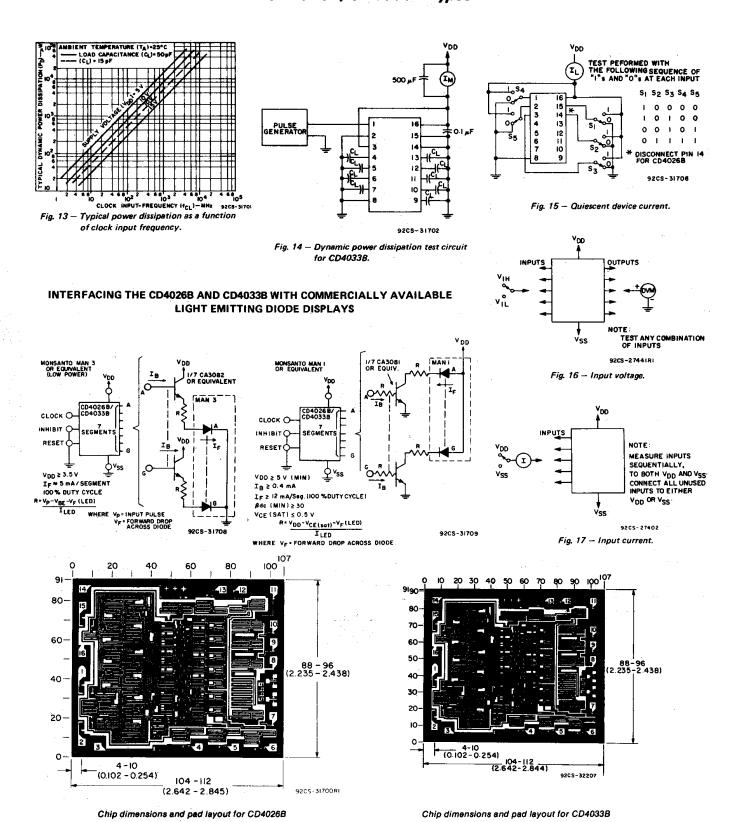

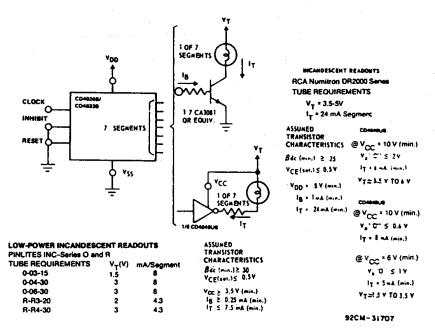

## INTERFACING THE CD4026B AND CD4033B WITH COMMERCIALLY AVAILABLE 7-SEGMENT DISPLAY DEVICES\*

<sup>e</sup> The interfacing buffers shown, while a necessity with the CD4026A and CD4033A, are not required when using the "B" devices; the "B" outputs (≈ 10 times the "A" outputs) can drive most display devices directly especially at voltages above 10 V.