# SERVICE MANUAL

CHASSIS NO.:CH-20

Please read this manual carefully before service.

# **TABLE OF CONTENTS**

| SAFETY INSTRUCTIONS                        | .1   |

|--------------------------------------------|------|

| ADJUSTMENTS                                | . 4  |

| STRUCTURE AND CHASSIS FUNCTION DESCRIPTION | . 17 |

| SERVICE DATA                               | . 17 |

| REPLACEMENT OF PARTS                       | . 55 |

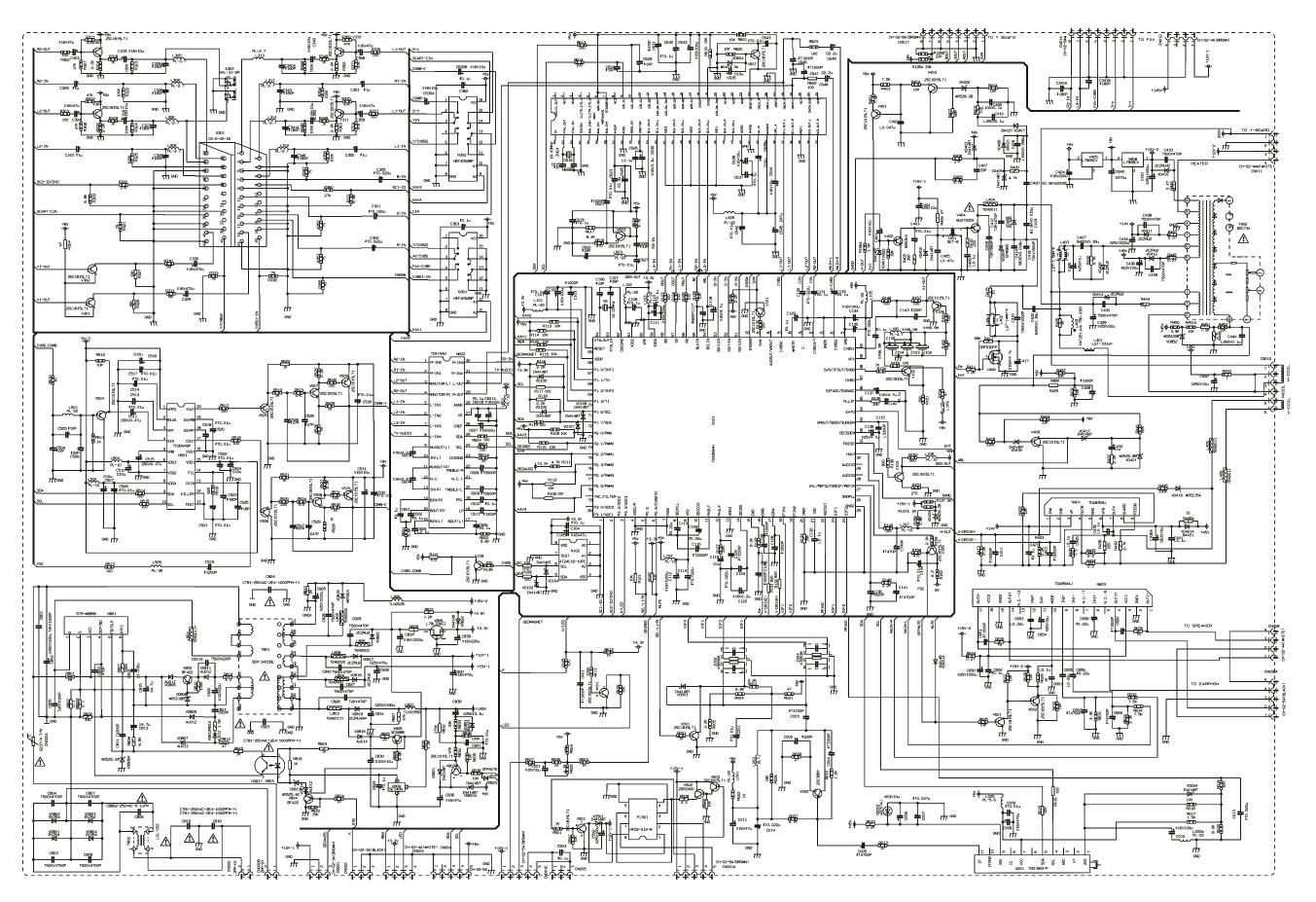

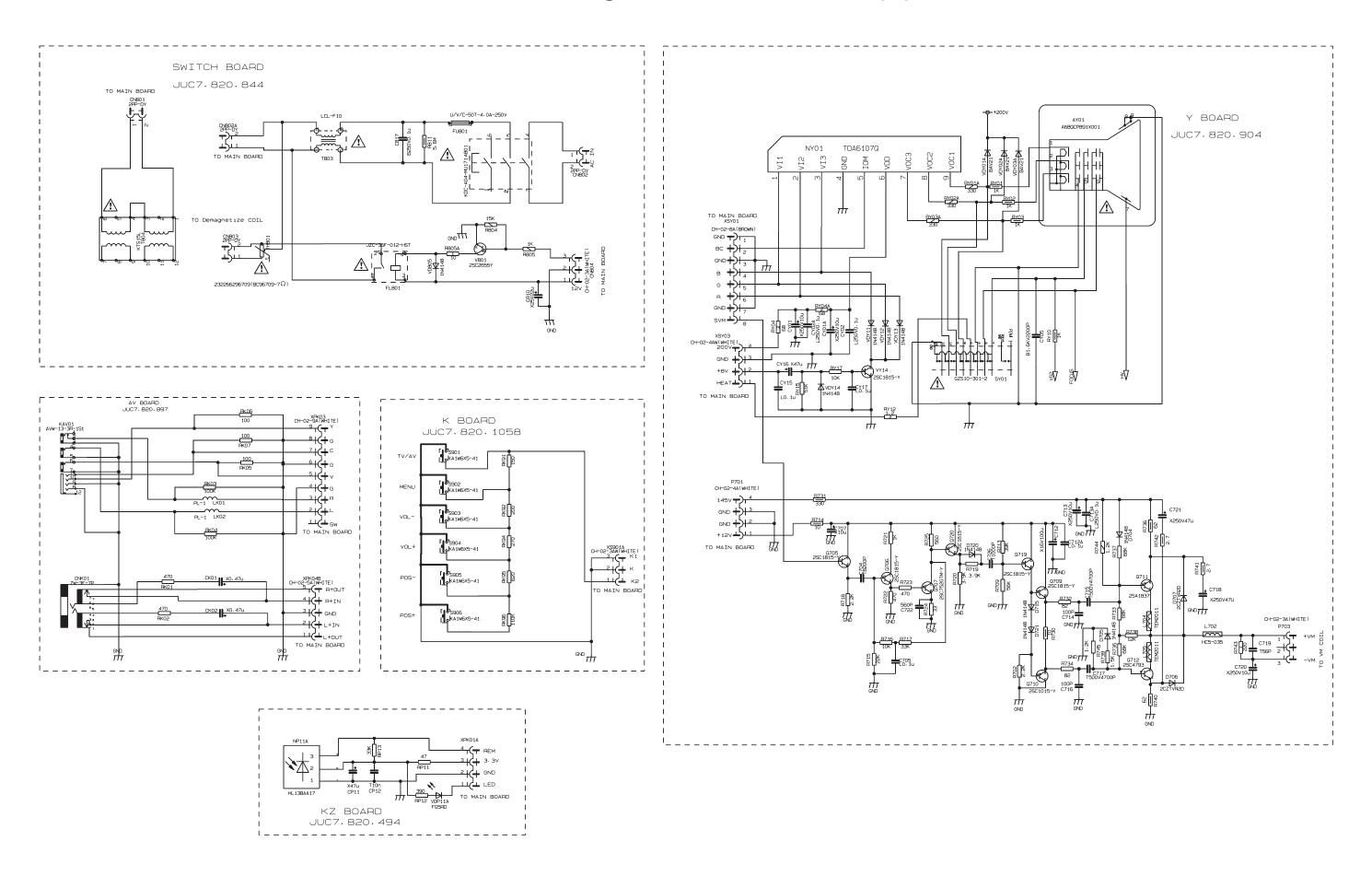

| APPENDIX CIRCUIT DIAGRAMS                  |      |

# INSTRUCTIONS FOR SERVICE SAFETY AND MAINTENANCE ADJUSTMENTS

WARNING: BEFORE SERVICING THIS CHASSIS, READ THE "X-RAY RADIATION PRECAUTION", "SAFETY PRECAUTION" AND "PRODUCT SAFETY NOTICE" INSTRUCTION BELOW.

#### X-RAY RADIATION PRECAUTION

- 1. The EHT must be checked every time the TV is serviced to ensure that the CRT does not emit X-ray radiation as result of excessive EHT voltage. The maximum EHT voltage permissible in any operating circumstances must not exceed the rated value. When checking the EHT, use the High Voltage Check procedure in this manual using an accurate EHT voltmeter.

- 2. The only source of X-RAY radiation in this TV is the CRT. The TV minimizes X-RAY radiation, which ensures safety during normal operation. To prevent X-ray radiation, the replacement CRT must be identical to the original fitted as specified in the parts list.

- 3. Some components used in this TV have safety related characteristics preventing the CRT from emitting X-ray radiation. For continued safety, replacement component should be made after referring the PRODUCT SAFETY NOTICE below.

- 4. Service and adjustment of the TV may result in changes in the nominal EHT voltage of the CRT anode. So ensure that the maximum EHT voltage does not exceed the rated value after service and adjustment.

#### SAFETY PRECAUTION

#### WARNING: REFER SERVICING TO QUALIFIED SERVICE PERSONNEL ONLY.

- 1. The TV has a nominal working EHT voltage. Extreme caution should be exercised when working on the TV with the back removed.

- 1.1 Do not attempt to service this TV if you are not conversant with the precautions and procedures for working on high voltage equipment.

- 1.2 When handling or working on the CRT, always discharge the anode to the TV chassis before removing the anode cap in case of electric shock.

- 1.3 The CRT, if broken, will violently expel glass fragments. Use shatterproof goggles and take extreme care while handling.

- 1.4 Do not hold the CRT by the neck as this is a very dangerous practice.

- 2. It is essential that to maintain the safety of the customer all power cord forms be replaced exactly as supplied from factory.

- 3. Voltage exists between the hot and cold ground when the TV is in operation. Install a suitable isolating transformer of beyond rated overall power when servicing or connecting any test equipment for the sake of safety.

- 4. When replacing ICs, use specific tools or a static-proof electric iron with small power (below 35W).

- 5. Do not use a magnetized screwdriver when tightening or loosing the deflection yoke assembly to avoid electronic gun magnetized and decrement in convergence of the CRT.

- When remounting the TV chassis, ensure that all guard devices, such as nonmetal control buttons, switch, insulating sleeve, shielding cover, isolating resistors and capacitors, are installed on the original place.

- 7. Replace blown fuses within the TV with the fuse specified in the parts list.

- 8. When replacing wires or components to terminals or tags, wind the leads around the terminal before soldering. When replacing safety components identified by the international hazard symbols on the circuit diagram and parts list, it must be the company-approved type and must be mounted as the original.

- 9. Keep wires away from high temperature components.

#### PRODUCT SAFETY NOTICE

CAUTION: FOR YOUR PROTECTION, THE FOLLOWING PRODUCT SAFETY NOTICE SHOULD BE READ CAREFULLY BEFORE OPERATING AND SERVICING THIS TV SET.

- 1. Many electrical and mechanical components in this chassis have special safety-related characteristics. These characteristics are often passed unnoticed by a visual inspection and the X-ray radiation protection afforded by them cannot necessarily be obtained by using replacements rated at higher voltages or wattage, etc. Components which have these special safety characteristics in this manual and its supplements are identified by the international hazard symbols on the circuit diagram and parts list. Before replacing any of these components read the parts list in this manual carefully. Substitute replacement components which do not have the same safety characteristics as specified in the parts list may create X-ray radiation.

- 2. Do not slap or beat the cabinet or CRT, since this may result in fire or explosion.

- 3. Never allow the TV sharing a plug or socket with other large-power equipment. Doing so may result in too large load, causing fire.

- 4. Do not allow anything to rest on or roll over the power cord. Protect the power cord from being walked on, modified, cut or pinched, particularly at plugs.

- 5. Do not place any objects, especially heavy objects and lightings, on top of the TV set. Do not install the TV near any heat sources such as radiators, heat registers, stove, or other apparatus that produce heat.

- 6. Service personnel should observe the SAFETY INSTRUCTIONS in this manual during use and servicing of this TV set. Otherwise, the resulted damage is not protected by the manufacturer.

#### SAFETY SYMBOL DESCRIPTION

The lightning symbol in the triangle tells you that the voltage inside this product may be strong enough to cause an electric shock. Extreme caution should be exercised when working on the TV with the back removed.

This is an international hazard symbol, telling you that the components identified by the symbol have special safety-related characteristics.

**FDA**

This symbol tells you that the critical components identified by the FDA marking have special safety-related characteristics.

**UL** This symbol tells you that the critical components identified by the UL marking

have special safety-related characteristics.

**C UL** This symbol tells you that the critical components identified by the C-UL marking have been evaluated to the UL and C-UL standards and have special safety-related characteristics.

**VDE** This symbol tells you that the critical components identified by the VDE marking have special safety-related characteristics.

#### **MAINTENANCE**

- 1. Place the TV set on a stable stand or base that is of adequate size and strength to prevent it from being accidentally tipped over, pushed off, or pulled off. Do not place the set near or over a radiator or heat register, or where it is exposed to direct sunlight.

- 2. Do not install the TV set in a place exposed to rain, water, excessive dust, mechanical vibrations or impacts.

- 3. Allow enough space (at least 10cm) between the TV and wall or enclosures for proper ventilation.

- 4. Slots and openings in the cabinet should never be blocked by clothes or other objects.

- 5. Please power off the TV set and disconnect it from the wall immediately if any abnormal condition are met, such as bad smell, belching smoke, sparkling, abnormal sound, no picture/sound/raster. Hold the plug firmly when disconnecting the power cord.

- 6. Unplug the TV set from the wall outlet before cleaning or polishing it. Use a dry soft cloth for cleaning the exterior of the TV set or CRT screen. Do not use liquid cleaners or aerosol cleaners.

# **ADJUSTMENTS**

#### **SET-UP ADJUSTMENTS**

The following adjustments should be made when a complete realignment is required or a new picture tube is installed.

Perform the adjustments in the following order:

- 1. Color purity

- 2. Convergence

- 3. White balance

#### Notes:

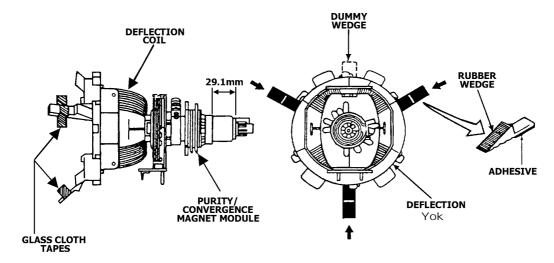

The purity/convergence magnet assembly and rubber wedges need mechanical positioning. Refer to Fig1, 2.

For some picture tubes, purity/ convergence adjustments are not required.

# 1. Color Purity Adjustment

Preparation:

Before starting this adjustment, adjust the vertical sync, horizontal sync, vertical amplitude and focus.

- 1.1 Face the TV set north or south.

- 1.2 Connect the power plug into the wall outlet and turn on the main power switch of the TV set.

- 1.3 Operate the TV for at least 15 minutes.

- 1.4 Degauss the TV set using a specific degaussing coil.

- 1.5 Set the brightness and contrast to maximum.

- 1.6 Counter clockwise rotate the R /B low brightness potentiometers to the end and rotate the green low brightness potentiometer to center.

- 1.7 Receive green raster pattern signals.

- 1.8 Loosen the clamp screw holding the deflection yoke assembly and slide it forward or backward to display a vertical green zone on the screen. Rotate and spread the tabs of the purity magnet around the neck of the CRT until the green zone is located vertically at the center of the screen.

- 1.9 Slowly move the deflection yoke assembly forward or backward until a uniform green screen is obtained.

- 1.10 Tighten the clamp screw of the assembly temporarily. Check purity of the red raster and blue raster until purities of the three rasters meet the requirement.

#### 2. Convergence Adjustment

#### Preparation:

Before attempting any convergence adjustment, the TV should be operated for at least 15 minutes.

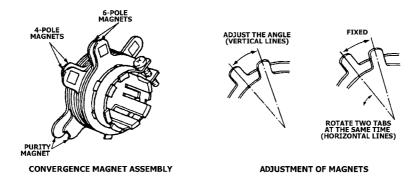

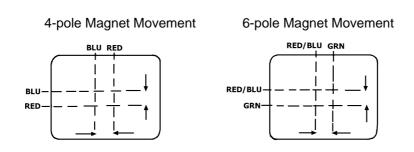

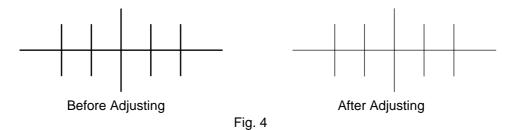

- 2.1 Center convergence adjustment

- 2.1.1 Receive dot pattern.

- 2.1.2 Adjust the brightness/contrast controls to obtain a sharp picture.

2.1.3 Adjust two tabs of the 4-pole magnet to change the angle between them and red and blue vertical lines are superimposed each other on the center of the screen.

Fig. 1

- 2.1.4 Turn both tabs at the same time keeping the angle constant to superimpose red and blue horizontal on the center of the screen.

- 2.1.5 Adjust two tabs of the 6-pole magnet to superimpose red/blue line and green line.

- 2.1.6 Remember red and blue movement. Repeat steps 2.1.3 ~ 2.1.5 until optimal convergence is obtained.

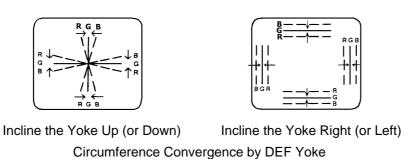

- 2.2 Circumference convergence adjustment

- 2.2.1 Loosen the clamp screw holding the deflection yoke assembly and allow it tilting.

- 2.2.2 Temporarily put the first wedge between the picture tube and deflection yoke assembly.

Move front of the deflection yoke up or down to obtain better convergence in circumference.

Push the mounted wedge in to fix the yoke temporarily.

- 2.2.3 Put the second wedge into bottom.

- 2.2.4 Move front of the deflection yoke to the left or right to obtain better convergence in circumference.

- 2.2.5 Fix the deflection yoke position and put the third wedge in either upper space. Fasten the deflection yoke assembly on the picture tube.

- 2.2.6 Detach the temporarily mounted wedge and put it in either upper space. Fasten the deflection yoke assembly on the picture tube.

- 2.2.7 After fastening the three wedges, recheck overall convergence and ensure to get optimal convergence. Tighten the lamp screw holding the deflection yoke assembly.

#### 3. White Balance Adjustment

Generally, white balance adjustment is made with professional equipment. It's not practical to get good white balance only through manual adjustment. For TVs with I<sup>2</sup>C bus control, change

the bus data to adjust white balance.

Fig. 2

Center Convergence by Convergence Magnets

Fig.3

#### **CIRCUIT ADJUSTMENTS**

#### **Preparation:**

Circuit adjustments should be made only after completion of set-up adjustments.

Circuit adjustments can be performed using the adjustable components inside the TV set. For TVs with I<sup>2</sup>C bus control, first change the bus data.

#### 1. Degaussing

A degaussing coil is built inside the TV set. Each time the TV is powered on, the degaussing coil will automatically degauss the TV. If the TV is magnetized by external strong magnetic field, causing color spot on the screen, use a specific degausser to demagnetize the TV in the following ways. Otherwise, color distortion will be shown on the screen.

- 1.1 Power on the TV set and operate it for at least 15 minutes.

- 1.2 Receive red full-field pattern.

- 1.3 Power on the specific degausser and face it to the TV screen.

- 1.4 Turn on the degausser. Slowly move it around the screen and slowly take it away from the TV.

- 1.5 Repeat the above steps until the TV is degaussed completely.

#### 2. Confirmation and Adjustment for Voltage

Caution: +B voltage has close relation to high voltage. To prevent X-ray radiation, set +B voltage to the rated value.

- 2.1 Power on the TV and receive Philips test pattern.

- 2.2 Check the resistors and coils for being burned. (If the fuse is burned out, do not power on the TV again until the cause is found out.)

- 2.3 Measure voltages of test points with the digital voltmeter. Measure the CRT high voltage with the high-voltage testing equipment and heater voltage with the high-frequency effective voltmeter. The rated values are shown as table 1

Table 1

| Test Point        | Voltage (V)            |

|-------------------|------------------------|

| One Pin of L807   | 145V ± 1.5V            |

| Positive of C834  | 12V ± 1V               |

| Positive of C837  | 12V ± 1V               |

| Positive of C832  | 16V ± 1V               |

| One Pin of L806   | 16V ± 1.5V             |

| Positive of C839  | $3.3 \pm 0.3 \text{V}$ |

| Positive of VD822 | $3.9 \pm 0.3 \text{V}$ |

| Positive of C429  | 195V ± 5V              |

| Positive of C436A | 48V ± 3V               |

| Positive of C434   | 13.5V ± 1V                   |

|--------------------|------------------------------|

| Positive of C840   | 8V ± 0.5V                    |

| One Pin of 326     | 12V ± 1V                     |

| Positive of C424   | 5V ± 0.5V                    |

| Heater             | 6.3V ± 0.3Vrms               |

| CPT anada valtagas | 29KV ± 1.5KV (For 29" CRT)   |

| CRT anode voltages | 31.0KV ± 1.5KV (For 34" CRT) |

# 3. High Voltage Inspection

Caution: No high voltage adjustment components inside the chassis. Please perform high voltage inspection in the following ways.

- 3.1 Connect a precise static high voltmeter to the second anode (inside the high voltage cap) of the CRT.

- 3.2 Plug in the supply socket (220V  $\sim$ , 50Hz) and turn on the TV. Set the brightness and contrast to minimum (0  $\mu$  A).

- 3.3 The high voltage reading should be less than the limited EHT voltage.

- 3.4 Change the brightness from minimum to maximum, and ensure high voltage not beyond the limitation in any case.

| Nominal EHT voltage | Limited EHT voltage | Remarks     |

|---------------------|---------------------|-------------|

| 29KV ± 1.5KV        | 33KV                | for 29" CRT |

| 31.0KV ± 1.5KV      | 35KV                | for 34" CRT |

Note: The data sheet may differ dependent on different CRTs.

#### 4. Focus Adjustment

Caution: Dangerously high voltages are present inside the TV. Extreme caution should be exercised when working on the TV with the back removed.

- 4.1 After removing the back cover, look for the FBT on the main PCB. There should be a FCB on the FBT.

- 4.2 Power on the TV and preheat it for 15 min.

- 4.3 Receive a normal TV signal. Rotate knob of the FCB until you get a sharp picture.

# 5. SERVICE mode

#### 5.1 To enter the SERVICE mode

Set the volume to 0 by the remote control. Then press and hold the MUTE button on the remote control and MENU button on the TV at the same time for over 2 seconds. In the S mode, press the POWER button to quit the S mode.

S

( "S" is red and other items are yellow.)

Use the / buttons on the remote control to highlight an adjustment and the / buttons to adjust it.

#### 5.2 Bus data

Table 2 Bus data

|           |                          | B 1.0                                        |

|-----------|--------------------------|----------------------------------------------|

| Item      | Adjustment               | Description                                  |

| VX00      | 19                       | 4:3                                          |

| VX50      | 01                       | 16:9                                         |

| VX99      | 38                       | ZOOM                                         |

| 5VS/6VS   | Set to the optimal mode  | Half vertical center for 50/60Hz             |

| 5VA/6VA   | Set to the optimal mode  | Vertical amplitude for 50/60Hz               |

| 5SC/6SC   | Set to the optimal mode  | Vertical S correction for 50/60Hz            |

| 5VSH/6VSH | Set to the optimal mode  | Vertical center for 50/60Hz                  |

| 5VOF/6VOF | Set to the optimal mode  | Character position for 50/60Hz               |

| 5HP/6HP   | Set to the optimal mode  | Parallelogram correction for 50/60Hz         |

| 5HB/6HB   | Set to the optimal mode  | Curve correction for 50/60Hz                 |

| 5HSH/6HSH | Set to the optimal mode  | Horizontal center for 50/60Hz                |

| 5HA/6HA   | Set to the optimal mode  | Horizontal amplitude for 50/60Hz             |

| 5EW/6EW   | Set to the optimal mode  | Pincushion and barrel correction for 50/60Hz |

| 5UCR/6UCR | Set to the optimal mode  | Upper corner correction for 50/60Hz          |

| 5LCR/6LCR | Set to the optimal mode  | Lower corner correction for 50/60Hz          |

| 5TC/6TC   | Set to the optimal mode  | Trapezoidal correction for 50/60Hz           |

| RCUT      | White balance adjustment | Red gun cutoff voltage                       |

| GCUT      | White balance adjustment | Green gun cutoff voltage                     |

| RDRV      | Dark balance adjustment  | Red gun drive voltage                        |

| GDRV      | Dark balance adjustment  | Green gun drive voltage                      |

| BDRV      | 20                       | Blue gun drive voltage                       |

| YDFP      | 8                        | PAL brightness delay time                    |

| YDFN      | 2                        | NTSC brightness delay time                   |

| YDFS      | 2                        | SECAM brightness delay time                  |

# SERVICE MANUAL

| RAGC   | Set to the optimal mode | AGC adjustment (19—1E recommended)          |  |  |  |  |

|--------|-------------------------|---------------------------------------------|--|--|--|--|

| VOL    | 29                      | AV output volume control for TDA7442        |  |  |  |  |

| WBF    | 30                      |                                             |  |  |  |  |

| WBR    | 30                      |                                             |  |  |  |  |

| SOC    | 1                       | PWL clip level (5%)                         |  |  |  |  |

| PWL    | 8                       | White peak limit                            |  |  |  |  |

| IFO    | 32                      | IF phase lock                               |  |  |  |  |

| PEAK   | 2                       |                                             |  |  |  |  |

| BLS    | 0                       | Blue extension                              |  |  |  |  |

| BKS    | 1                       | Black stretch                               |  |  |  |  |

| CON100 | 23                      | O. h. continued                             |  |  |  |  |

| CON50  | 0D                      | Sub contrast                                |  |  |  |  |

| BRI100 | 32                      | Cult building                               |  |  |  |  |

| BRI50  | 20                      | Sub brightness                              |  |  |  |  |

| COL100 | 3F                      | Sub color                                   |  |  |  |  |

| SHP100 | 3B                      | Cult all amaza                              |  |  |  |  |

| SHP50  | 1C                      | Sub sharpness                               |  |  |  |  |

| VMDL   | 03                      | VM delay                                    |  |  |  |  |

| VMAM   | 03                      | VM amplitude                                |  |  |  |  |

| COR    | 3                       |                                             |  |  |  |  |

| WS     | 0                       | White stretch setting                       |  |  |  |  |

| HDOL   | 0B                      | Cathode drive level                         |  |  |  |  |

| AGCS   | 1                       | AGC speed                                   |  |  |  |  |

| VG2B   | 24                      | Brightness setting when adjusting G2        |  |  |  |  |

| VENH   | 03                      | Vertical enhance                            |  |  |  |  |

| CBNR   | 03                      | Comb noise reduce                           |  |  |  |  |

| TRE1   | 64                      | Table line with                             |  |  |  |  |

| TRE2   | 32                      | Treble linearity                            |  |  |  |  |

| BAS1   | 64                      | Door lineagit.                              |  |  |  |  |

| BAS2   | 32                      | Bass linearity                              |  |  |  |  |

| VOLA   | 40/53                   | MSP3410G/TDA7442                            |  |  |  |  |

| VOLB   | 46/58                   | MSP3410G/TDA7442                            |  |  |  |  |

| VOLC   | 4B/60                   | MSP3410G/TDA7442                            |  |  |  |  |

| VOLD   | 51/63                   | MSP3410G/TDA7442                            |  |  |  |  |

| LOUD   | 20                      | Loudness (not for TDA7442)                  |  |  |  |  |

| SC1    | 74                      | SCART1 PRESCAL (not for TDA7442)            |  |  |  |  |

| SC2    | 74                      | SCART2 PRESCAL (not for TDA7442)            |  |  |  |  |

| SCIN   | 1E                      | SCART IN PRESCAL (not for TDA7442)          |  |  |  |  |

| FMIN   | 13                      | FM frequency bias setting (not for TDA7442) |  |  |  |  |

| NNIN   | 5A                      | NICAM setting (not for TDA7442)             |  |  |  |  |

# SERVICE MANUAL

| WOCF | 1E                          | ( not for TDA7442)            |  |  |  |

|------|-----------------------------|-------------------------------|--|--|--|

| MEFF | 44                          |                               |  |  |  |

| MAMP | FF                          |                               |  |  |  |

| MHAR | 64                          | MDB setting (not for TDA7442) |  |  |  |

| MLOP | 19                          |                               |  |  |  |

| MHIP | 05                          |                               |  |  |  |

| OP1  | F8 (For PF29T18/34t18 only) | Option set byte 1             |  |  |  |

| OFT  | D8 (For CPF29T99 only)      | Option set byte 1             |  |  |  |

| OP2  | 20                          | Option set byte 2             |  |  |  |

| OP3  | 0C                          | Option set byte 3             |  |  |  |

| OP4  | 11                          | Option set byte 4             |  |  |  |

| OP5  | 88                          | Option set byte 5             |  |  |  |

| OP6  | 0F                          | Option set byte 6             |  |  |  |

| OP7  | 08                          | Option set byte 7             |  |  |  |

# Notes:

The data sheet may differ dependent on different models.

The data sheet may differ dependent on different CRTs for the same model.

Designs and specifications are subject to change without notice.

**Table 3 Option bit setting**

|          | Bit | Item         | Description            |  |  |  |  |  |

|----------|-----|--------------|------------------------|--|--|--|--|--|

|          | 0   | OP_NICAM     | 1: MSP3410; 0: TDA7442 |  |  |  |  |  |

|          | 1   | OP_COMB      | 1: Yes; 0: No          |  |  |  |  |  |

|          | 2   | OP_SVM       | 1: Yes; 0: No          |  |  |  |  |  |

|          | 3   | OP_AV2       | 1: Yes; 0: No          |  |  |  |  |  |

| OP1      | 4   | OP_FAV       | 1: Yes; 0: No          |  |  |  |  |  |

|          | 5   | OP_FAVS      | 1: Yes; 0: No          |  |  |  |  |  |

|          |     | OD CTODE     | 0: West Europe         |  |  |  |  |  |

|          | 6   | OP_STORE     | 1: East Europe         |  |  |  |  |  |

| 7 OP_OSO |     |              | 1                      |  |  |  |  |  |

|          | 0   | OD AVC       | 1: MSP3410;            |  |  |  |  |  |

|          |     | OP_AVC       | 0: TDA7442             |  |  |  |  |  |

|          | 1   | OD MDD       | 1: MSP3410;            |  |  |  |  |  |

|          | 1   | OP_MDB       | 0: TDA7442             |  |  |  |  |  |

| OP2      | 2   |              | 000: West Europe text  |  |  |  |  |  |

| OFZ      |     | <u> </u>     | 001: East Europe text  |  |  |  |  |  |

|          | 3   | Text setting | 010: Ukrainian text    |  |  |  |  |  |

|          |     | 1            | 100: Russian text      |  |  |  |  |  |

|          | 4   |              | 110: Greek text        |  |  |  |  |  |

|          | 5   | OP_ PARENT   | 1 (Child lock)         |  |  |  |  |  |

|      | 6 | OP_TILT       | Tilt correction                                                                                                                  |  |  |  |  |  |

|------|---|---------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|      | 7 | OP_FSL        | 0                                                                                                                                |  |  |  |  |  |

|      | 0 | OP_BSCREEN    | <ul><li>1: Black screen available when changing channels;</li><li>0: Black screen not available when changing channels</li></ul> |  |  |  |  |  |

|      | 1 | OP_5060       | 0                                                                                                                                |  |  |  |  |  |

| OP3  | 2 | OP_DK         | 1: D/K option                                                                                                                    |  |  |  |  |  |

|      | 3 | OP_BG         | 1: B/G option                                                                                                                    |  |  |  |  |  |

|      | 4 | OP_I          | 1: I option                                                                                                                      |  |  |  |  |  |

|      | 5 | OP_L          | 1: L option                                                                                                                      |  |  |  |  |  |

|      | 6 | OP_AUTO_SOUND | 1: MSP3410 ; 0: TDA7442                                                                                                          |  |  |  |  |  |

|      | 7 | OP_EQUAL      | 1: MSP3410; 0: TDA7442                                                                                                           |  |  |  |  |  |

|      | 0 | OP_FMWS       | 1                                                                                                                                |  |  |  |  |  |

|      | 1 | OP_POWER      | 1: Memory on 0: Soft on                                                                                                          |  |  |  |  |  |

|      | 2 | OP_COUNTRY    | 1: COUNTRY display option                                                                                                        |  |  |  |  |  |

|      | 3 | OP_LOGO       | 0: LOGO display not available                                                                                                    |  |  |  |  |  |

| OP4  | 4 | OP_DFL        | 1                                                                                                                                |  |  |  |  |  |

|      | 5 | OP_BLUE_BACK  | Blue back not available under no signal condition;     Blue back available under no signal condition                             |  |  |  |  |  |

|      | 6 | OP_ACI        | 1: Yes; 0: No                                                                                                                    |  |  |  |  |  |

|      | 7 | OP_ATS        | 1: Yes; 0: No                                                                                                                    |  |  |  |  |  |

|      | 0 | OP_LANG0      | 0                                                                                                                                |  |  |  |  |  |

|      | 1 | OP_LANG1      | 0                                                                                                                                |  |  |  |  |  |

|      | 2 | OP_LANG2      | 0                                                                                                                                |  |  |  |  |  |

| OP5  | 3 | OP_LANG3      | 0                                                                                                                                |  |  |  |  |  |

| OF 3 | 4 | OP_SOUND0     | 0                                                                                                                                |  |  |  |  |  |

|      | 5 | OP_SOUND1     | 0                                                                                                                                |  |  |  |  |  |

|      | 6 | OP_SOUND2     | 1                                                                                                                                |  |  |  |  |  |

|      | 7 | OP_STRIKE     | 1                                                                                                                                |  |  |  |  |  |

|      | 0 | OP_MUTE       | 1                                                                                                                                |  |  |  |  |  |

|      | 1 | OP_TUNER      | 1: West Europe 0: BG                                                                                                             |  |  |  |  |  |

|      | 2 | OP_AFT        | 1                                                                                                                                |  |  |  |  |  |

| OP6  | 3 | OP_ENGLISH    | 1                                                                                                                                |  |  |  |  |  |

|      | 4 | OP_FRANCE     | 1                                                                                                                                |  |  |  |  |  |

|      | 5 | OP_GERMAN     | 1                                                                                                                                |  |  |  |  |  |

|      | 6 | OP_SPAIN      | 1                                                                                                                                |  |  |  |  |  |

|      | 7 | OP_DANMARK    | 1                                                                                                                                |  |  |  |  |  |

|     | 0 | OP_HOLAND  | 1 |

|-----|---|------------|---|

|     | 1 | OP_SUOMI   | 1 |

|     | 2 | OP_GREECE  | 1 |

| OD7 | 3 | OP_ITALY   | 1 |

| OP7 | 4 | OP_NORWAY  | 1 |

|     | 5 | OP_PORTUAL | 1 |

|     | 6 | OP_SWEDEN  | 1 |

|     | 7 | OP_TURKY   | 1 |

#### Note:

Bit6, Bit5, Bit4 in OP5 are outgoing audio option settings as follows: 000: East Europe (D/K); 001: West Europe (B/G); 010: UK (I); 110: France (L); 100: Europe (Auto). Bit3, Bit2, Bit1 and Bit0 in OP5 are outgoing language option settings as follows: English, French, German, Spanish, Danish, Dutch, Finnish, Greek, Italian, Norwegian, Portuguese, Swedish and Turkish successively begun with.

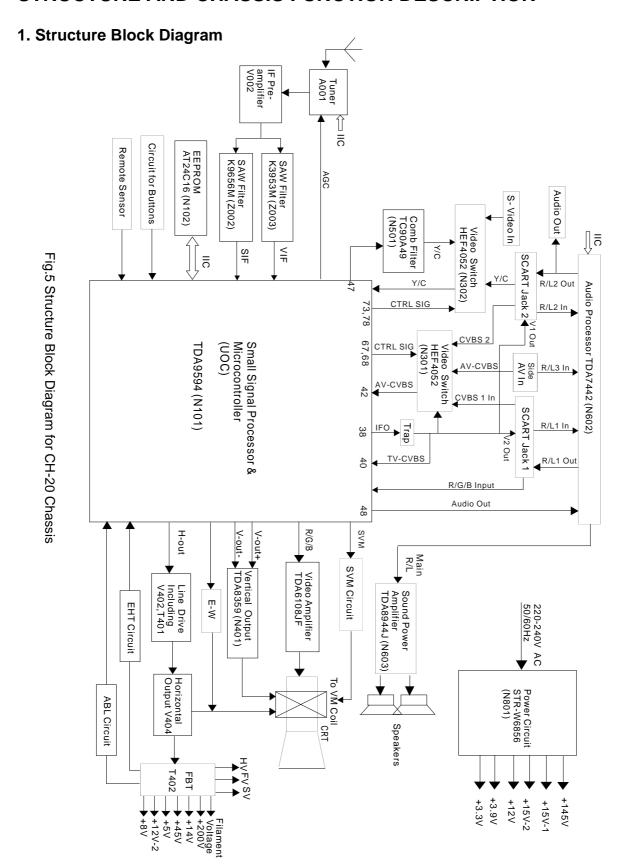

# STRUCTURE AND CHASSIS FUNCTION DESCRIPTION

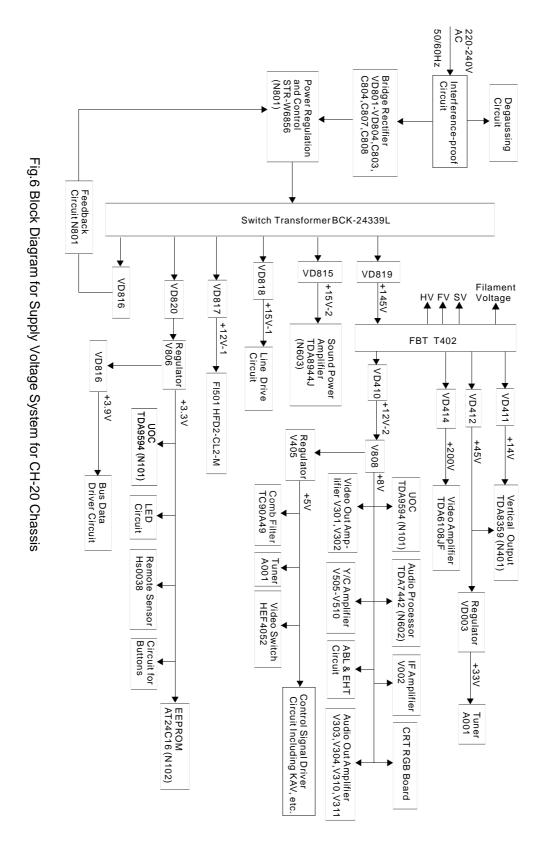

# 2. Block Diagram for Supply Voltage System

# 3. Chassis Description

#### **General Description**

CH-20 chassis is applied in CPF29T99/PF29T18/34T18, which mainly uses Philips' advanced UOC-ultimate one chip TDA959X and I<sup>2</sup>C-bus controlled IC. With combination of microcontroller and small signal processor, the TDA959X features high-integrity, high-performance-to-price ratio and high-reliability and advanced functions with fewer external components, which provide much more convenience for manufacturing and technical service. In addition, TDA959X is good in geometric distortion, more suitable for pure flat TV sets.

#### The following features are available in the chassis:

RF color systems: PAL/SECAM

Video systems: PAL/SECAM/NTSC

Sound systems: D/K B/G I H L L1

●100 programs preset

•I<sup>2</sup>C bus control

● Audio output: Main channel: 7W+7W (distortionless) (THD 7%)

• Selectable sound modes: Music, Theatre, Speech, Personal

• Selectable picture modes: Personal, Rich, Natural, Soft

●AV stereo + audio processing (MSP34XX or TDA7442)

● PAL/NTSC 3-line comb filter

Earphone output

• Selectable aspect ratio: 4:3, 16:9, Zoom

Auto identification and changeover of vertical frequency 50/60Hz

● Auto identification of SCART picture input format (4:3,16:9)

Auto identification of SCART1 signal source input (RGB/CVBS)

#### The chassis mainly uses the following ICs and assemblies.

Table 4 Key ICs and Assemblies

| Serial No. | Position  | Туре                 | Function Description                             |  |  |  |  |

|------------|-----------|----------------------|--------------------------------------------------|--|--|--|--|

| 1          | N101      | TDA9594H             | Microcontroller and small signal processor (UOC) |  |  |  |  |

| 2          | N102      | AT24C16              | EEPROM                                           |  |  |  |  |

| 3          | N602      | TDA7442              | Audio processor                                  |  |  |  |  |

| 4          | N603      | TDA8944J             | Sound power amplifier                            |  |  |  |  |

| 5          | NY01      | TDA6107JF /TDA6108JF | Video amplifier                                  |  |  |  |  |

| 6          | N501      | TC90A49P             | COMB Filter                                      |  |  |  |  |

| 7          | N301/N302 | HEF4052BP            | Electronic switch circuit                        |  |  |  |  |

| 8          | N401      | TDA8359J             | Vertical scan output stage circuit               |  |  |  |  |

| 9          | N801      | STR-W6856            | Power module                                     |  |  |  |  |

| 10         | A001      | TDQ-6B3-P/ TAF5-EPB2 | Tuner                                            |  |  |  |  |

# **SERVICE DATA**

# 1. Technical Data of Key ICs

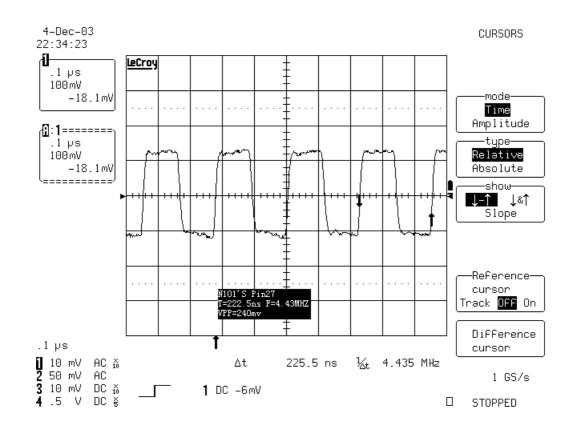

#### 1.1 Microcontroller and Small Signal Processor TDA959X

#### (1) General Description

The various versions of the TDA959X H/PS-N1 series combine the functions of a video processor together with a m-Controller and US Closed Caption decoder. Most versions have a Teletext decoder on board. The Teletext decoder has an internal RAM memory for 1 or 10 page text. Some versions can generate a 'Mixed-down' I-signal for the demodulation of DVB signals. The ICs are intended to be used in economy television receivers with 110 picture tubes.

The ICs have supply voltages of 8 V and 3.3 V and they are mounted in an SDIP-64 or QFP 80 envelope.

The features are given in the following feature list. The differences between the various ICs are given in the table.

#### (2) Features

#### TV-signal processor

#### Available in all versions

- Multi-standard vision IF circuit with alignment-free PLL demodulator

- Internal (switchable) time-constant for the IF-AGC circuit

- Integrated chrominance trap circuit Integrated luminance delay line with adjustable delay time

- Picture improvement features with peaking (with switchable centre frequency, depeaking, variable positive/negative overshoot ratio and video dependent coring), dynamic skin tone control and blue- and black stretching

- Scan Velocity Modulation output

- Integrated chroma band-pass filter with switchable centre frequency

- Only one reference (12 MHz) crystal required for the m-Controller, Teletext- and the colour decoder

- Multi-standard colour decoder with automatic search system

- Internal base-band delay line

- Indication of the Signal-to-Noise ratio of the incoming CVBS signal

- A linear RGB/YUV/YPBPR input with fast blanking for external RGB/YUV sources. The synchronization circuit can be connected to the incoming Y signal. The Text/OSD signals are internally supplied from the m-Controller/Teletext decoder.

- RGB Cathode Calibration', white point and black level off-set adjustment so that the colour temperature of the dark and the light parts of the screen can be chosen independently.

- Contrast reduction possibility during mixed-mode of OSD and Text signals

- Adjustable 'wide blanking' of the RGB outputs

- Horizontal synchronization with two control loops and alignment-free horizontal oscillator

- Vertical count-down circuit

- Vertical driver optimized for DC-coupled vertical output stages

- Horizontal and vertical geometry processing

- Horizontal and vertical zoom function for 16: 9 applications

- Horizontal parallelogram and bow correction for large screen picture tubes

- · Low-power start-up of the horizontal drive circuit

#### Available in S-DIP 64 versions

• Source selection between the 'internal' CVBS and an external CVBS or Y/C signal

#### Available in QFP-80 versions

- The mono intercarrier sound circuit has a selective FM-PLL demodulator which can be switched to the different FM sound frequencies (4.5/5.5/6.0/6.5 MHz). The quality of this system is such that the external band-pass filters can be omitted.

- The FM-PLL demodulator can be set to centre frequencies of 4.74/5.74 MHz so that a second sound channel can be demodulated. In such an application it is necessary that an external bandpass filter is inserted.

The vision IF and mono intercarrier sound circuit can be used for the demodulation of FM radio signals

- The QSS and mono FM functionality are both available so that an FM/AM TV receiver can be built without the use of additional ICs

- Video switch with 2 external CVBS inputs and a CVBS output. One of the CVBS inputs can be used as Y/C input.

- 2 external audio inputs. The selection of the various inputs is coupled to the selection of the CVBS signals

- Switchable group delay correction in the CVBS path

- White stretching and a switchable DC transfer ratio for the luminance signal

#### m-Controller

- 80C51 m-controller core standard instruction set and timing

- 1 ms machine cycle

- 32 128Kx8-bit late programmed ROM

- 3 12Kx8-bit Auxiliary RAM (shared with Display)

- Interrupt controller for individual enable/disable with two level priority

- Two 16-bit Timer/Counter registers

- One 16-bit Timer with 8-bit Pre-scaler

- WatchDog timer

- Auxiliary RAM page pointer

- 16-bit Data pointer

- Stand-by, Idle and Power Down modes

- 14 bits PWM for Voltage Synthesis Tuning

- 8-bit A/D converter with 4 multiplexed inputs

- 5 PWM (6-bits) outputs for control of TV analogue signals

#### **Data Capture**

- Text memory for 1 or 10 pages

- In the 10 page versions inventory of transmitted Teletext pages stored in the Transmitted Page Table (TPT) and Subtitle Page Table (SPT)

- Data Capture for US Closed Caption

- Data Capture for 525/625 line WST, VPS (PDC system A) and Wide Screen Signalling (WSS) bit decoding

- Automatic selection between 525 WST/625 WST

- Real-time capture and decoding for WST Teletext in Hardware, to enable optimized m-processor

- Automatic selection between 625 WST/VPS on line 16 of VBI

- throughput

- Automatic detection of FASTEXT transmission

- Real-time packet 26 engine in Hardware for processing accented, G2 and G3 characters

- Signal quality detector for video and WST/VPS data types

- Comprehensive teletext language coverage

- Full Field and Vertical Blanking Interval (VBI) data

- capture of WST data

#### **Display**

- Teletext and Enhanced OSD modes

- Features of level 1.5 WST and US Close Caption

- Serial and Parallel Display Attributes

- Single/Double/Quadruple Width and Height for characters

- Scrolling of display region

- Variable flash rate controlled by software

- Enhanced display features including overlining, underlining and italics

- Soft colours using CLUT with 4096 colour palette

- Globally selectable scan lines per row (9/10/13/16) and character matrix [12x10, 12x13, 12x16 (VxH)]

- Fringing (Shadow) selectable from N-S-E-W direction

- Fringe colour selectable

- Meshing of defined area

- Contrast reduction of defined area

- Cursor

- Special Graphics Characters with two planes, allowing four colours per character

- 32 software redefinable On-Screen display characters

- 4 WST Character sets (G0/G2) in single device (e.g. Latin, Cyrillic, Greek, Arabic)

- G1 Mosaic graphics, Limited G3 Line drawing characters

- WST Character sets and Closed Caption Character set in single device

# (3) Functional Difference between the Various IC Versions

# Table 5

| IC Version (TDA)                                                                                    | 9590PS | 9591PS  | 9592PS | 9593PS | 9594PS  | 9590H | 9591H   | 9592H | 9593H  | 9594H   |

|-----------------------------------------------------------------------------------------------------|--------|---------|--------|--------|---------|-------|---------|-------|--------|---------|

| TV range                                                                                            | 110    | 110     | 110    | 110    | 110     | 110   | 110     | 110   | 110    | 110     |

| Mono intercarrier multi-standard sound demodulator (4.5 - 6.5 MHz) with switchable centre frequency |        |         |        |        |         |       |         |       |        |         |

| Audio switch                                                                                        |        |         |        |        |         |       |         |       |        |         |

| Automatic Volume Leveling or subcarrier output (for comb filter applications)                       |        |         |        |        |         |       |         |       |        |         |

| QSS sound IF amplifier with separate input and AGC circuit                                          |        |         |        |        |         |       |         |       |        |         |

| AM sound demodulator without extra reference circuit                                                |        |         |        |        |         |       |         |       |        |         |

| Generation of a 'Mixed-down' I-signal for the demodulation of DVB signals                           |        |         |        |        |         |       |         |       |        |         |

| FM radio option (via QSS amplifier)                                                                 |        |         |        |        |         |       |         |       |        |         |

| FM radio option (with FM tuner)                                                                     |        |         |        |        |         |       |         |       |        |         |

| PAL decoder                                                                                         |        |         |        |        |         |       |         |       |        |         |

| SECAM decoder                                                                                       |        |         |        |        |         |       |         |       |        |         |

| NTSC decoder                                                                                        |        |         |        |        |         |       |         |       |        |         |

| Horizontal geometry (E-W)                                                                           |        |         |        |        |         |       |         |       |        |         |

| Horizontal and vertical zoom                                                                        |        |         |        |        |         |       |         |       |        |         |

| ROM size                                                                                            | 64 k   | 64-28k  | 64 k   | 32-64k | 64-128k | 64 k  | 64-28k  | 64 k  | 32-64k | 64-128k |

| User RAM size                                                                                       | 2 k    | 2 k     | 2 k    | 2 k    | 2 k     | 2 k   | 2 k     | 2 k   | 2 k    | 2 k     |

| Teletext                                                                                            |        | 10 page |        | 1 page | 10 page |       | 10 page |       | 1 page | 10 page |

| Closed captioning                                                                                   |        |         |        |        |         |       |         |       |        |         |

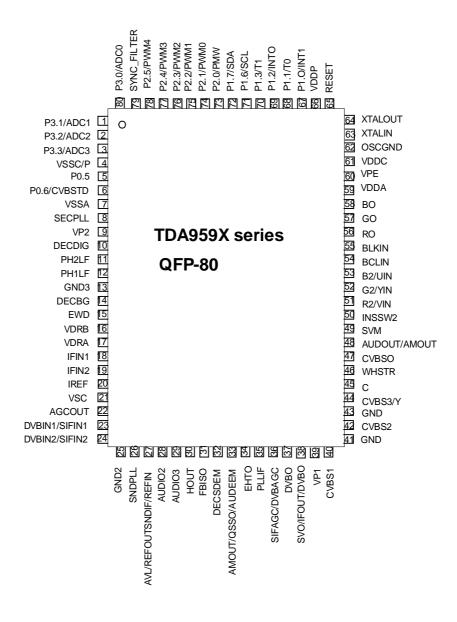

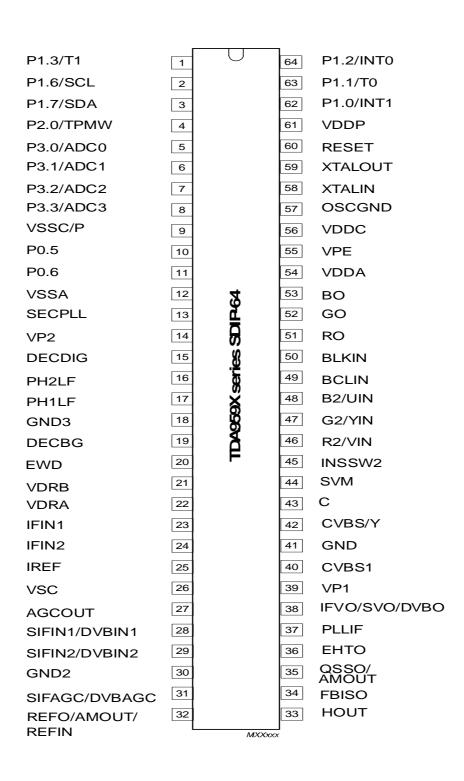

# (4) Pinning (QFP-80 ENVELOPE)

| Symbol                                 | Pin            |         | Description                                                                                                                                                             |

|----------------------------------------|----------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| - Cyminoti                             | QFP-80 SDIP-64 |         |                                                                                                                                                                         |

| P3.1/ADC1                              | 1              | 6       | port 3.1 or ADC1 input                                                                                                                                                  |

| P3.2/ADC2                              | 2              | 7       | port 3.2 or ADC2 input                                                                                                                                                  |

| P3.3/ADC3                              | 3              | 8       | port 3.3 or ADC3 input                                                                                                                                                  |

| VSSC/P                                 | 4              |         | digital ground for m-Controller core and periphery                                                                                                                      |

| P0.5                                   | 5              | 10      | port 0.5 (8 mA current sinking capability for direct drive of LEDs)                                                                                                     |

| P0.6/CVBSTD                            | 6              | 11      | port 0.6 (8 mA current sinking capability for direct drive of LEDs) or Composite video input. A positive-going 1V(peak-to-peak) input is required                       |

| VSSA                                   | 7              | 12      | digital ground of TV-processor                                                                                                                                          |

| SECPLL                                 | 8              |         | SECAM PLL decoupling                                                                                                                                                    |

| VP2                                    | 9              |         | 2nd supply voltage TV-processor (+8V)                                                                                                                                   |

| DECDIG                                 | 10             |         | supply voltage decoupling of digital circuit of TV-processor                                                                                                            |

| PH2LF                                  | 11             |         | phase-2 filter                                                                                                                                                          |

| PH1LF                                  | 12             |         | phase-1 filter                                                                                                                                                          |

| GND3                                   | 13             |         | ground 3 for TV-processor                                                                                                                                               |

| DECBG                                  | 14             |         | bandgap decoupling                                                                                                                                                      |

| EWD                                    | 15             |         | East-West drive output                                                                                                                                                  |

| VDRB                                   | 16             |         | vertical drive B output                                                                                                                                                 |

| VDRA                                   | 17             |         | vertical drive A output                                                                                                                                                 |

| IFIN1                                  | 18             |         | IF input 1                                                                                                                                                              |

| IFIN2                                  | 19             |         | IF input 2                                                                                                                                                              |

| IREF                                   | 20             |         | reference current input                                                                                                                                                 |

| VSC                                    | 21             |         | vertical sawtooth capacitor                                                                                                                                             |

| AGCOUT                                 | 22             |         | tuner AGC output                                                                                                                                                        |

| SIFIN1/DVBIN1 (1)                      | 23             |         | SIF input 1 / DVB input 1                                                                                                                                               |

| SIFIN2/DVBIN2 (1)                      | 24             |         | SIF input 2 / DVB input 2                                                                                                                                               |

| GND2                                   | 25             |         | ground 2 for TV processor                                                                                                                                               |

| SNDPLL<br>AVL/REF0/SNDIF/<br>REFIN (1) | 26<br>27       | 32      | narrow band PLL filter Automatic Volume Levelling / subcarrier reference output / sound IF input / external reference signal input for I signal mixer for DVB operation |

| AUDIO2                                 | 28             |         | audio 2 input                                                                                                                                                           |

| AUDIO3                                 | 29             |         | audio 3 input                                                                                                                                                           |

| HOUT                                   | 30             |         | horizontal output                                                                                                                                                       |

| FBISO                                  | 31             |         | flyback input/sandcastle output                                                                                                                                         |

| DECSDEM<br>QSSO/AMOUT/<br>AUDEEM (1)   | 32<br>33       | -<br>35 | decoupling sound demodulator QSS intercarrier output / AM output in stereo applications or deemphasis (front-end audio out) / AM output in mono applications            |

| EHTO                                   | 34             |         | EHT/over voltage protection input                                                                                                                                       |

| PLLIF                                  | 35             |         | IF-PLL loop filter                                                                                                                                                      |

| SIFAGC/DVBAGC (1)                      |                |         | AGC sound IF / internal-external AGC for DVB applications                                                                                                               |

| INTCO/DVBO (1)                         | 37             |         | intercarrier output (from QSS or vision IF amplifier) / DVB output                                                                                                      |

| IFVO/SVO/DVBO (1)                      | 38             |         | IF video output / selected CVBS output / DVB output                                                                                                                     |

| VP1                                    | 39             |         | main supply voltage TV processor                                                                                                                                        |

| CVBS1                                  | 40             |         | internal CVBS input                                                                                                                                                     |

| GND                                    | 41             |         | ground for TV processor                                                                                                                                                 |

| טאוט                                   | 41             | 41      | ground for 1 v processor                                                                                                                                                |

| Symbol        | Pin    |         | Description                                                                                           |

|---------------|--------|---------|-------------------------------------------------------------------------------------------------------|

|               | QFP-80 | SDIP-64 | ·                                                                                                     |

| CVBS2         | 42     |         | external CVBS2 input                                                                                  |

| GND           | 43     | •       | ground for TV-processor                                                                               |

| CVBS3/Y       | 44     | 42      | CVBS3/Y input                                                                                         |

| С             | 45     | 43      | chroma input                                                                                          |

| WHSTR         | 46     | -       | white stretch capacitor                                                                               |

| CVBSO         | 47     | -       | CVBS output                                                                                           |

| AUDOUT /AMOUT | 48     | 1       | audio output /AM audio output (volume controlled)                                                     |

| SVM           | 49     | 44      | scan velocity modulation output                                                                       |

| INSSW2        | 50     | 45      | 2nd RGB / YUV insertion input                                                                         |

| R2/VIN        | 51     | 46      | 2nd R input / V (R-Y) input / PR input                                                                |

| G2/YIN        | 52     | 47      | 2nd G input / Y input                                                                                 |

| B2/UIN        | 53     | 48      | 2nd B input / U (B-Y) input / PB input                                                                |

| BCLIN         | 54     | 49      | beam current limiter input                                                                            |

| BLKIN         | 55     | 50      | black current input / V-guard input                                                                   |

| RO            | 56     | 51      | Red output                                                                                            |

| GO            | 57     | 52      | Green output                                                                                          |

| ВО            | 58     | 53      | Blue output                                                                                           |

| VDDA          | 59     | 54      | analog supply of Teletext decoder and digital supply of TV-processor (3.3 V)                          |

| VPE           | 60     | 55      | OTP Programming Voltage                                                                               |

| VDDC          | 61     | 56      | digital supply to core (3.3 V)                                                                        |

| OSCGND        | 62     | 57      | oscillator ground supply                                                                              |

| XTALIN        | 63     | 58      | crystal oscillator input                                                                              |

| XTALOUT       | 64     | 59      | crystal oscillator output                                                                             |

| RESET         | 65     | 60      | reset                                                                                                 |

| VDDP          | 66     | 61      | digital supply to periphery (+3.3 V)                                                                  |

| P1.0/INT1     | 67     | 62      | port 1.0 or external interrupt 1 input                                                                |

| P1.1/T0       | 68     | 63      | port 1.1 or Counter/Timer 0 input                                                                     |

| P1.2/INT0     | 69     | 64      | port 1.2 or external interrupt 0 input                                                                |

| P1.3/T1       | 70     | 1       | port 1.3 or Counter/Timer 1 input                                                                     |

| P1.6/SCL      | 71     | 2       | port 1.6 or I <sup>2</sup> C-bus clock line                                                           |

| P1.7/SDA      | 72     | 3       | port 1.7 or I <sup>2</sup> C-bus data line                                                            |

| P2.0/TPWM     | 73     | 4       | port 2.0 or Tuning PWM output                                                                         |

| P2.1/PWM0     | 74     | -       | port 2.1                                                                                              |

| P2.2/PWM1     | 75     | -       | port 2.2                                                                                              |

| P2.3/PWM2     | 76     | -       | port 2.3                                                                                              |

| P2.4/PWM3     | 77     | -       | port 2.4                                                                                              |

| P2.5/PWM4     | 78     | -       | port 2.5                                                                                              |

| SYNC_FILTER   | 79     | 1       | CVBS (i.e. P0.6/CVBS) Sync filter input: This pin should be connected to VSSA via a 100 nF capacitor. |

| P3.0/ADC0     | 80     | 5       | port 3.0 or ADC0 input                                                                                |

# Note:

<sup>1.</sup> The functional content of these pins is dependent on the envelope (SDIP-64 or QFP-80), the mode of operation and on some  $I^2$ C-bus control bits.

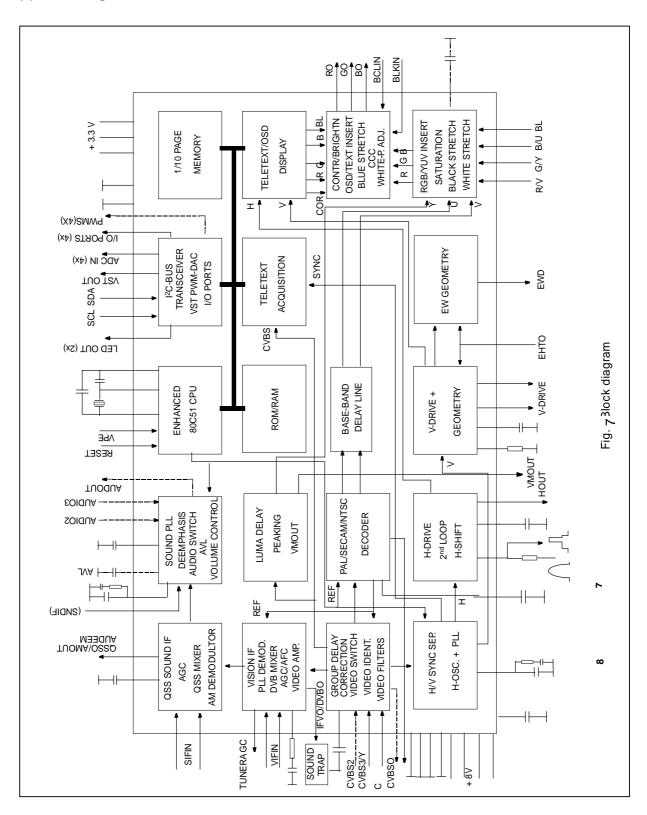

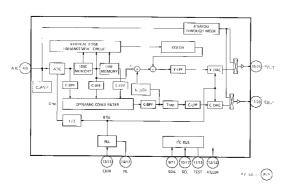

# (5) Black Diagram

# (6) Pining

Fig. 8 Pin configuration (QFP-80)

Fig. 9 Pin configuration (SDIP 64)

(7) Refer to Table 12 about Functions and Data of the IC's Pins.

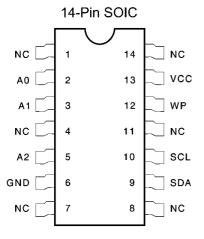

#### 1.2 EEPROM AT24C16 (N101)

#### (1) Features

- Low Voltage and Standard Voltage Operation

$5.0 (V_{CC} = 4.5V \text{ to } 5.5V)$

$2.7 (V_{CC} = 2.7V \text{ to } 5.5V)$

$2.5 (V_{CC} = 2.5 \text{V to } 5.5 \text{V})$

$1.8 (V_{CC} = 1.8V \text{ to } 5.5V)$

- Internally Organized 128 x 8 (1K), 256 x 8 (2K),

512 x 8 (4K),1024 x 8 (8K) or 2048 x 8 (16K)

- · 2-Wire Serial Interface

- Bidirectional Data Transfer Protocol

- 100 kHz (1.8V, 2.5V, 2.7V) and 400 kHz (5V)

Compatibility

- · Write Protect Pin for Hardware Data Protection

- 8-Byte Page (1K, 2K), 16-Byte Page (4K, 8K, 16K) Write Modes

- · Partial Page Writes Are Allowed

- Self-Timed Write Cycle (10 ms max)

- · High Reliability

Endurance: 1 Million Cycles

Data Retention: 100 Years

Automotive Grade and Extended Temperature Devices Available

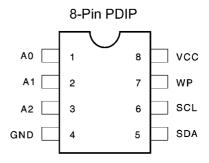

#### (3) Pin Configurations

| Pin Name                         | Function           |

|----------------------------------|--------------------|

| A <sub>0</sub> to A <sub>2</sub> | Address Inputs     |

| SDA                              | Serial Data        |

| SCL                              | Serial Clock Input |

| WP                               | Write Protect      |

| NC                               | No Connect         |

8-Pin and 14-Pin JEDEC SOIC and 8-Pin

PDIP Packages

# (2) Description

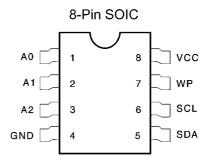

The AT24C01A/02/04/08/16 provides 1024/2048/4096/8192/16384 bits of serial electrically erasable and programmable read only memory (EEPROM) organized as 128/256/512/1024/2048 words of 8 bits each. The device is optimized for use in many industrial and commercial applications where low power and low voltage operation are essential. The AT24C01A/02/04/08/16 is available in space saving 8-pin PDIP, 8-pin and 14-pin SOIC packages and is accessed via a 2-wire serial interface. In addition, the entire family is available in 5.0V (4.5V to 5.5V), 2.7V (2.7V to 5.5V), 2.5V (2.5V to 5.5V) and 1.8V (1.8V to 5.5V) versions.

Fig. 10

# (4) Block Diagram

(5) Refer to Table 13 about Functions and Data of the IC's Pins.

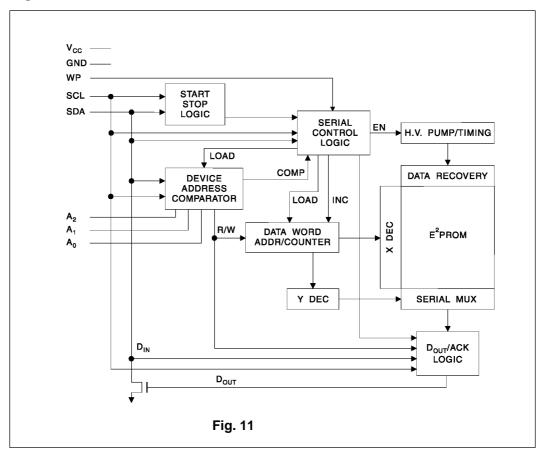

#### 1.3 Tone Control and Surround Digitally Controlled Audio Processor TDA7442/TDA7442D

#### (1) Features

4 Stereo Inputs

Input Attenuation Control In 0.5db Step

Treble And Bass Control

Two Surround Mode Available With 4 Selectabler Responses:

- Music

- Simulated Stereo

Two Speaker Attenuators:

- 2 Independent Speaker Controls

In 1db Steps For Balance Facility

- Independent Mute Function All Functions Programmable Via Serial Bus

- 2 Monitor Output (Only For Tda7442)

# (2) Description

The TDA7442/42D is volume tone (bass and treble) balance (Left/Right) processors for quality audio applications in TV and Hi-Fi systems. It reproduces surround sound by using a programmable phase shifter. Control of all the functions is accomplished by serial bus.

The AC signal setting is obtained by resistor networks and switches combined with operational amplifiers.

Thanks to the BIPOLAR/CMOS Technology used, Low Distortion, Low Noise and DC stepping are obtained.

#### (3) Pin Connections

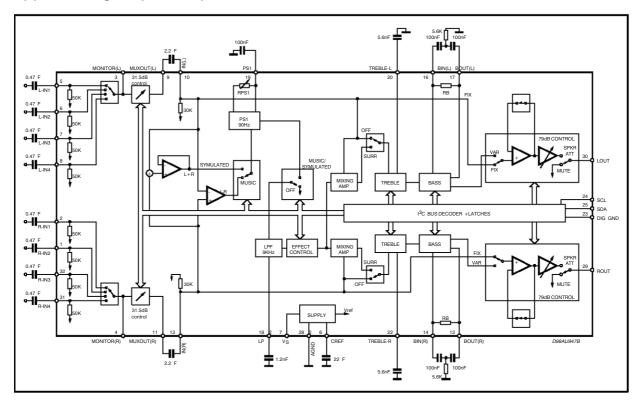

# (4) Block Diagram (TDA7442)

# (5) Block Diagram (TDA7442D)

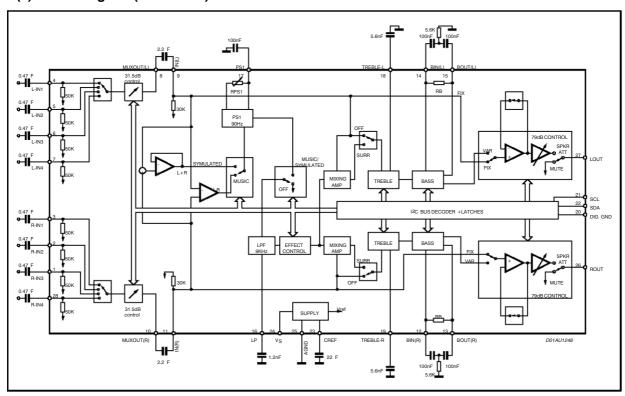

#### 1.4 Sound Power Amplifier TDA8944J (N603)

#### (1) General Description

The TDA8944J is a dual-channel audio power amplifier with an output power of  $2\times7$  W at an  $8\Omega$  load and a 12V supply. The circuit contains two Bridge Tied Load (BTL) amplifiers with an all-NPN output stage and standby/mute logic. The TDA8944J comes in a 17-pin DIL-bent-SIL (DBS) power package. The TDA8944J is printed-circuit board (PCB) compatible with all other types in the TDA894x family. One PCB footprint accommodates both the mono and the stereo products.

#### (2) Features

- · Few external components

- · Fixed gain

- Standby and mute mode

- · No on/off switching plops

- · Low standby current

- · High supply voltage ripple rejection

- · Outputs short-circuit protected to ground, supply and across the load

- · Thermally protected

- · Printed-circuit board compatible.

#### (3) Block Diagram

Fig. 10 Block Diagram

#### **Pinning**

Fig. 11 Pin Configuration.

#### (4) Refer to Table 14 about functions and Service Data of the IC's Pin's

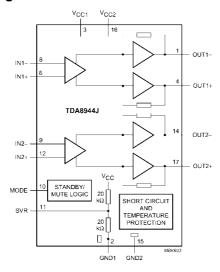

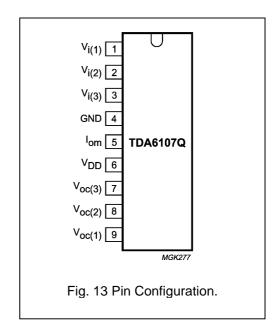

#### 1.5 Triple Video Output Amplifier TDA6108JF/6107Q

#### (1) Features

Typical bandwidth of 9.0MHz (for TDA6108JF) or 5.5MHz (for TDA6107Q) for an output signal of 60 V (peak-to-peak value)

- High slew rate of 1850V/ µs (for TDA6108JF) or 900V/ µs (for TDA6107Q)

- · No external components required

- · Very simple application

- · Single supply voltage of 200 V

- · Internal reference voltage of 2.5 V

- Fixed gain of 51 (for TDA6108JF) or 50 (for TDA6107Q)

- · Black-Current Stabilization (BCS) circuit

- · Thermal protection.

#### (2) General Description

The TDA6107Q/6108JF includes three video output amplifiers in one plastic DIL-bent-SIL 9-pin medium power (DBS9MPF) package (SOT 111-1), using high-voltage DMOS technology, and is intended to drive the three cathodes of a colour CRT directly. To obtain maximum performance, the amplifier should be used with black-current control.

# (3) Ordering Information

Table 6

| Туре                   | Package |                                                             |          |  |

|------------------------|---------|-------------------------------------------------------------|----------|--|

| Number                 | Name    | Description                                                 | Version  |  |

| TDA6108JF/<br>TDA6107Q | DBS9MPF | Plastic DIL-bent-SIL medium power package with fin; 9 leads | SOT111-1 |  |

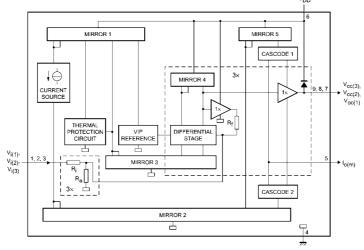

#### (4) Block Diagram

Fig. 12

Table 7 Pinning

| Symbol             | Pin | Description        |

|--------------------|-----|--------------------|

| V <sub>i(1)</sub>  | 1   | Inverting input 1  |

| V <sub>i(2)</sub>  | 2   | Inverting input 2  |

| V <sub>i(3)</sub>  | 3   | Inverting input 3  |

| GND                | 4   | ground (fin)       |

|                    | 5   | Black-current      |

| l <sub>om</sub>    |     | measurement output |

| $V_{DD}$           | 6   | Supply voltage     |

| V <sub>oc(3)</sub> | 7   | Cathode output 3   |

| V <sub>oc(2)</sub> | 8   | Cathode output 2   |

| V <sub>oc(1)</sub> | 9   | Cathode output 1   |

(5) Refer to Table 15 about Functions and Data of the IC's Pins.

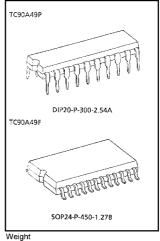

### 1.6 COMB Filter TC90A49P (N1)

#### (1) Features

- TV format: NTSC (3.58), PAL, M-PAL, and N-PAL

- · Dynamic comb filter

- · Vertical edge enhancement circuit

- PLL 8 x multiplier circuit

- · Internal 8-bit 4 fsc AD converter

- Internal 8-bit precision 8 fsc DA converter (2 ch)

- · Sync tip clamp circuit

- · Internal 4H-line memory

- I<sup>2</sup>C bus interface

- Package : DIP 20-pin and SOP 24-pin

- · 5V single power supply

Weight

DIP20-P-300-2.54A : 1.11 g (Typ.)

SOP24-P-450-1.27B : 0.44 g (Typ.)

Fig. 14

#### (2) Block Diagram

Fig. 15

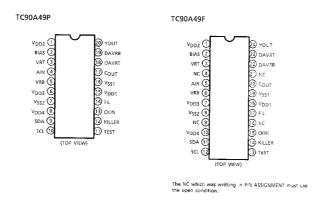

# (3) Pin Assignment

Fig. 16

# (4) Refer to Table 16 about Functions and Service Data of the IC's Pins.

#### 1.7 Dual 4-channel Analog Multiplexer/Demultiplexer HEF4052

#### (1) Description

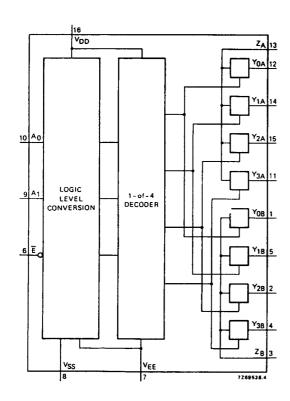

The HEF4052 is a dual 4-channel analog multiplexer/demultiplexer with common channel select logic. Each multiplexer/demultiplexer has four independent inputs/outputs ( $Y_0$  to  $Y_3$ ) and a common input/output (Z). The common channel select logic includes two address inputs ( $A_0$  and  $A_1$ ) and an active LOW enable input (E).

Both multiplexers/demultiplexers contain four bidirectional analog switches, each with one side connected to an independent input/output  $(Y_0 \text{ to } Y_3)$  and the other side connected to a common input/output(Z).

With  $\overline{E}$  LOW, one of the four switches is selected (low impedance ON-state) by  $A_0$  and  $A_1$ . With E HIGH,  $\overline{A}$  switches are in the high impedance OFF-state, independent of  $A_0$  and  $A_1$ .  $V_{DD}$  and  $V_{SS}$  are the supply voltage connections for the digital control inputs ( $A_0$ ,  $A_1$  and E). The  $V_{DD}$  to  $V_{SS}$  range is 3 to 15 V. The analog inputs/outputs ( $Y_0$  to  $Y_3$ , and Z) can swing between  $V_{DD}$  as a positive limit and  $V_{EE}$  as a negative limit.

V<sub>DD</sub> V<sub>EE</sub> may not exceed 15 V.

For operation as a digital multiplexer/demultiplexer,  $V_{\text{EE}}$  is connected to  $V_{\text{SS}}$  (typically ground)

#### (2) Block Diagrams

Fig. 17

Table 8 Pinning

| Y <sub>OA</sub> to Y <sub>3A</sub> | Independent inputs/outputs |

|------------------------------------|----------------------------|

| Y <sub>OB</sub> to Y <sub>3B</sub> | Independent inputs/outputs |

| A <sub>O</sub> A <sub>1</sub>      | Address inputs             |

| E                                  | Enable input (active LOW)  |

| Z <sub>A</sub> Z <sub>B</sub>      | Common inputs/outputs      |

Family data, I<sub>DD</sub> LIMITS category MSI

See Family Specifications

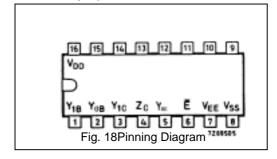

HEF4052P (N): 16-lead DIL; plastic

(SOT38-1)

HEF4052D (F): 16-lead DIL; ceramic (cerdip) (SOT74)

HEF4052T (D): 16-lead SO; plastic

(SOT109-1)

(): Package Designator North America

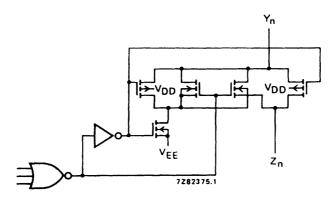

Fig. 19 Schematic Diagram (One Switch)

## (3) Function Table

Table 9

| Inputs |                |       | Channel                                                           |

|--------|----------------|-------|-------------------------------------------------------------------|

| Е      | A <sub>1</sub> | $A_0$ | On                                                                |

| L      | L              | L     | $Y_{OA}$ - $Z_A$ ; $Y_{OB}$ - $Z_B$                               |

| L      | L              | Н     | $Y_{1A}$ - $Z_A$ ; $Y_{1B}$ - $Z_B$                               |

| L      | Н              | L     | Y <sub>2A</sub> -Z <sub>A</sub> ; Y <sub>2B</sub> -Z <sub>B</sub> |

| L      | Н              | Н     | $Y_{3A}$ - $Z_A$ ; $Y_{3B}$ - $Z_B$                               |

| Н      | Х              | Х     | none                                                              |

### **Notes**

H=HIGH state (the more positive voltage) L=LOW state (the less positive voltage)

X=state is immaterial

#### **Ratings**

Limiting values in accordance with the Absolute Maximum System (IEC 134) Supply voltage (with reference to  $V_{DD}$ )  $V_{EE}$  -18 to +0,5 V

#### Note

To avoid drawing  $V_{DD}$  current out of terminal Z, when switch current flows into terminals Y, the voltage drop across the bidirectional switch must not exceed 0,4V. If the switch current flows into terminal Z, no  $V_{DD}$  current will flow out of terminals Y, in this case is no limit for the voltage drop across the switch, but the voltages at Y and Z may not exceed  $V_{DD}$  or  $V_{EE}$

## (4) Refer to Table 17 about Functions and Data of the IC's Pins.

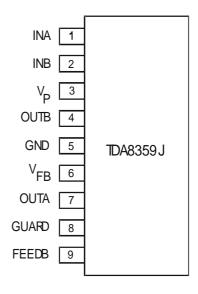

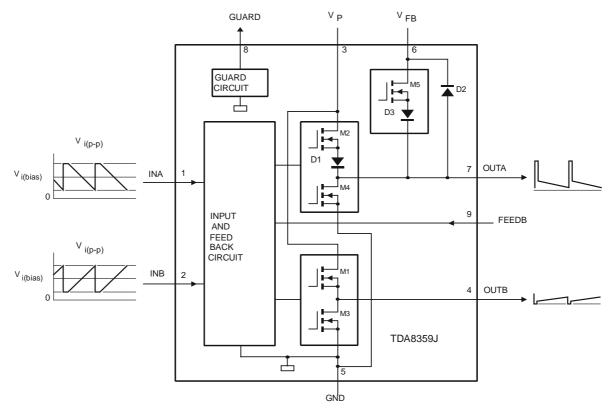

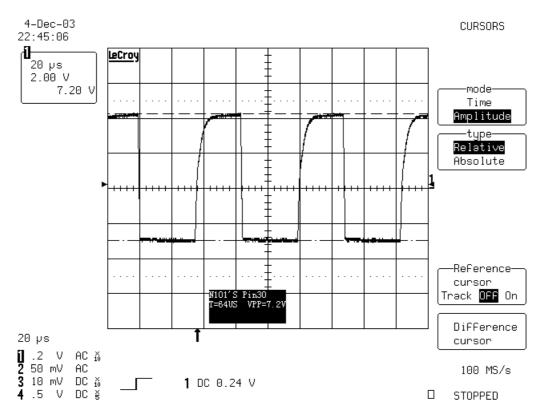

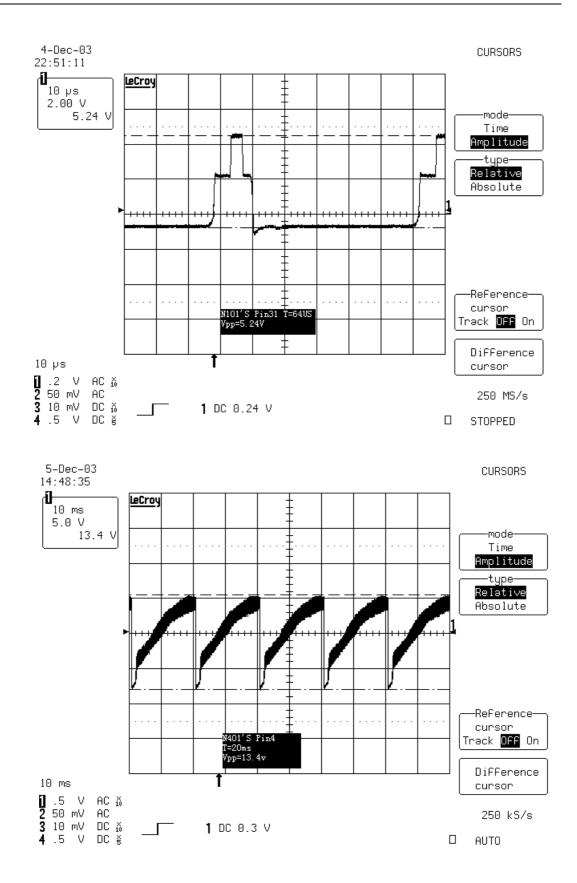

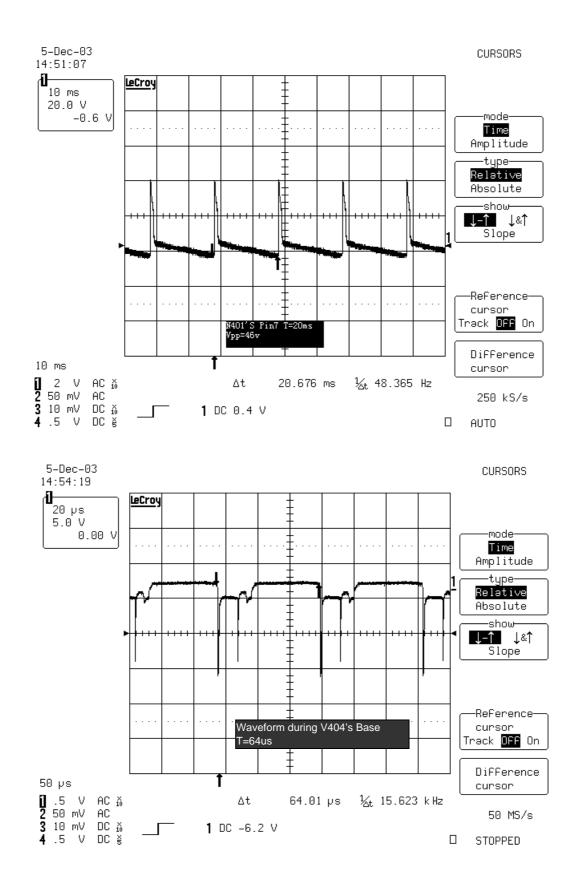

## 1.8 Vertical deflection output TDA8359J

## (1) Introduction

The TDA8359J is an integrated power circuit for use in 90° and 110° colour deflection systems. It contains a vertical deflection bridge output, operating as a high efficiency class G system and can handle field frequencies from 25 to 200 Hz. The vertical coil of a 4 : 3 as well a 16 : 9 picture tube can be connected to this vertical deflection device. Due to the bridge configuration a DC deflection output application can be designed with a positive main supply of typical 12 Volts and a positive flyback supply of typical 45 Volt. (Depending on the coil data).

This integrated circuit is designed in a Low Voltage DMOS (LVDMOS) process that combines bipolar, CMOS and DMOS components. DMOS output transistors (MOSFETs) are used because of the absence of secondary breakdown, which gives a better SOAR performance. The internal circuits are designed in such way that only a few external components are needed to get a correct working application.

The TDA8359J is functional the same as the TDA8357J vertical deflection output stage. The TDA8359J differs in only one aspect from the TDA8357J, it is able to deliver a higher output current which is more suitable for large picture tubes.

A detailed investigation procedure to determine an optimum application is given at the end of this report.

### (2) Features

- · Few external components required

- · High efficiency fully DC coupled vertical bridge output circuit

- · Short rise and fall time of the vertical flyback switch

- · Picture tube burn in protection signal (guard circuit)

- · Temperature (thermal) protection circuit

- · Differential mode inputs

- Blanking pulse generator (guard)

- · Improved EMC performance due to differential inputs

### (3) Pinning

Table 10

| Symbol | Pin | Description            |

|--------|-----|------------------------|

| INA    | 1   | Input A                |

| INB    | 2   | Input B                |

| VP     | 3   | Supply voltage         |

| OUTB   | 4   | Output B               |

| GND    | 5   | Ground                 |

| VFB    | 6   | Flyback supply voltage |

| OUTA   | 7   | Output A               |

| GUARD  | 8   | Guard output           |

| FEEDB  | 9   | Feedback input         |

Fig. 20

# (3) Block Diagram

Fig. 21

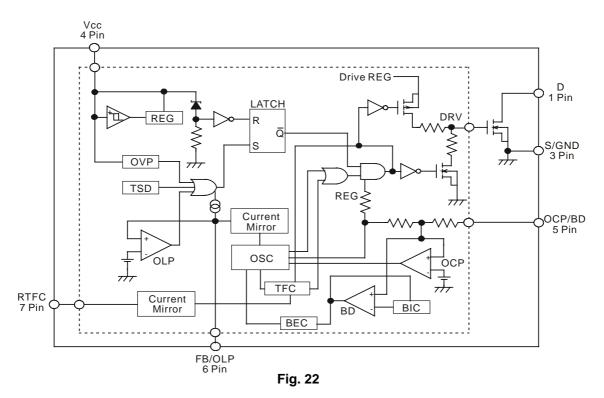

## 1.9 Switch-mode Power Supply STR- W68XX

#### (1) General Description

The STR-W6800 Series are thick-film ICs for Quasi-Resonant flyback SMPS with MOSFET and control built-in, featuring fewer external components, simplified circuit design, small-size and standard power supply.

"STR-W6800 Series ICs" offers three operation modes: Quasi-Resonant, Multi-Bottom Skip and Time Fix Control, thus guaranteeing high efficiency in all loading areas by means of the automatic change-over of the operation modes.

QR---- Quasi-Resonant operation at the time of heavy load

MBS---- Multi-Bottom Skip operation at the time of medium load for preventing oscillating frequency rising up and fixing operating frequency

TFC---- Time Fix Control at the time of light load such as stand-by load

By adopting chip-on-chip construction, even small package can deal with big power.

### (2) Features

- Seven-pin small SIP style package FM207 (generally called TO220), affording dielectric isolation

- Guarantees space of 1.8mm between high voltage pin and other pins, thus high voltage MOSFET built-in allowed

- Offers low startup current by employing BCD-Process