### TL500I, TL500C, TL501I, TL501C, TL502C, TL503C ANALOG-TO-DIGITAL-CONVERTER BUILDING BLOCKS

D2477 DECEMBER 1979 - REVISED JANUARY 1989

### TL500I, TL500C, TL501I, TL501C ANALOG PROCESSORS

- True Differential Inputs

- Automatic Zero

- Automatic Polarity

- High Input Impedance . . . 10<sup>9</sup> Ohms Typically

### TL500I, TL500C CAPABILITIES

- Resolution . . .14 Bits (with TL502C)

- Linearity Error . . . 0.001%

- 4 1/2-Digit Readout Accuracy with External Precision Reference

### TL502C/TL503C DIGITAL PROCESSORS

- Fast Display Scan Rates

- Internal Oscillator May Be Driven or Free-Running

- Interdigit Blanking

- Over-Range Blanking

- 4 1/2-Digit Display Circuitry

- High-Sink-Current Digit Driver for Large Displays

### TL5011, TL501C CAPABILITIES

- Resolution . . . 10-13 Bits (with TL502C)

- Linearity Error . . . 0.01%

- 3 1/2-Digit Readout Accuracy

### **TL502C CAPABILITIES**

- Compatible with Popular Seven-Segment Common-Anode Displays

- High-Sink-Current Segment Driver for Large Displays

### **TL503C CAPABILITIES**

- Multiplexed BCD Outputs

- High-Sink-Current BCD Outputs

Caution. These devices have limited built-in gate protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### description

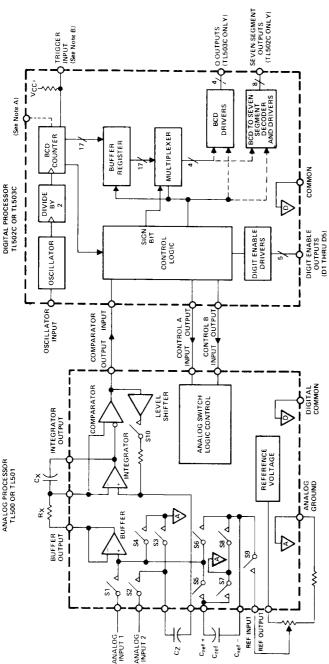

The TL500I, TL500C, TL501I, and TL501C analog processors and TL502C and TL503C digital processors provide the basic functions for a dual-slope-integrating analog-to-digital converter.

The TL500 and TL501 contain the necessary analog switches and decoding circuits, reference voltage generator, buffer, integrator, and comparator. These devices may be controlled by the TL502C, TL503C, by discrete logic, or by a software routine in a microprocessor.

The TL502C and TL503C each includes oscillator, counter, control logic, and digit enable circuits. The TL502C provides multiplexed outputs for seven-segment displays, while the TL503C has multiplexed BCD outputs.

When used in complementary fashion, these devices form a system that features automatic zero-offset compensation, true differential inputs, high input impedance, and capability for 4 1/2-digit accuracy. Applications include the conversion of analog data from high-impedance sensors of pressure, temperature, light, moisture, and position. Analog-to-digital-logic conversion provides display and control signals for weight scales, industrial controllers, thermometers, light-level indicators, and many other applications.

Texas V Instruments Copyright © 1979, Texas Instruments Incorporated

# TL500I, TL500C, TL501I, TL501C, TL502C, TL503C ANALOG-TO-DIGITAL-CONVERTER BUILDING BLOCKS

### principles of operation

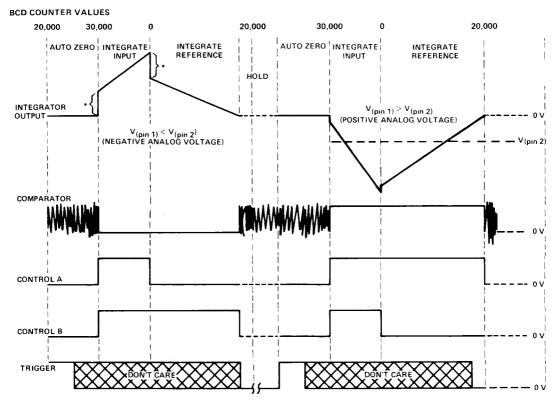

The basic principle of dual-slope-integrating converters is relatively simple. A capacitor,  $C_X$ , is charged through the integrator from  $V_{CT}$  for a fixed period of time at a rate determined by the value of the unknown voltage input. Then the capacitor is discharged at a fixed rate (determined by the reference voltage) back to  $V_{CT}$  where the discharge time is measured precisely. The relationship of the charge and discharge values are shown below (see Figure 1).

$$V_{CX} = V_{CT} - \frac{V_{I}t_1}{R_X C_X}$$

Charge (1)

$$V_{CT} = V_{CX} - \frac{V_{ref} t_2}{R_X C_X}$$

Discharge (2)

Combining equations 1 and 2 results in:

$$\frac{V_{I}}{V_{ref}} = -\frac{t_2}{t_1} \tag{3}$$

where:

VCT = Comparator (offset) threshold voltage

VCX = Voltage change across CX during t1 and during t2 (equal in magnitude)

V<sub>I</sub> = Average value of input voltage during t<sub>1</sub>

t<sub>1</sub> = Time period over which unknown voltage is integrated

t<sub>2</sub> = Unknown time period over which a known reference voltage is integrated.

Equation (3) illustrates the major advantages of a dual-slope converter:

- a. Accuracy is not dependent on absolute values of t<sub>1</sub> and t<sub>2</sub>, but is dependent on their ratios. Long-term clock frequency variations will not affect the accuracy.

- b. Offset values, VCT, are not important.

The BCD counter in the digital processor (see Figure 2) and the control logic divide each measurement cycle into three phases. The BCD counter changes at a rate equal to one-half the oscillator frequency.

### auto-zero phase

The cycle begins at the end of the integrate-reference phase when the digital processor applies low levels to inputs A and B of the analog processor. If the trigger input is at a high level, a free-running condition exists and continuous conversions are made. However, if the trigger input is low, the digital processor stops the counter at 20,000, entering a hold mode. In this mode, the processor samples the trigger input every 4000 oscillator pulses until a high level is detected. When this occurs, the counter is started again and is carried to completion at 30,000. The reference voltage is stored on reference capacitor  $C_{\rm ref}$ , comparator offset voltage is stored on integration capacitor  $C_{\rm X}$ , and the sum of the buffer and integrator offset voltages is stored on zero capacitor  $C_{\rm Z}$ . During the auto-zero phase, the comparator output is characterized by an oscillation (limit cycle) of indeterminate waveform and frequency that is filtered and d-c shifted by the level shifter.

### integrate-input phase

The auto-zero phase is completed at a BCD count of 30,000, and high levels are applied to both control inputs to initiate the integrate-input phase. The integrator charges  $C_X$  for a fixed time of 10,000 BCD counts at a rate determined by the input voltage. Note that during this phase, the analog inputs see only the high impedance of the noninverting operational amplifier input. Therefore, the integrator responds only to the difference between the analog input terminals, thus providing true differential inputs.

### integrate-reference phase

At a BCD count of 39,999 + 1 = 40,000 or 0, the integrate-input phase is terminated and the integrate-reference phase is begun by sampling the comparator output. If the comparator output is low corresponding to a negative average analog input voltage, the digital processor applies a low and a high to inputs A and B, respectively, to apply the reference voltage stored on C<sub>ref</sub> to the buffer. If the comparator output is high corresponding to a positive input, inputs A and B are made high and low, respectively, and the negative of the stored reference voltage is applied to the buffer. In either case, the processor automatically selects the proper logic state to cause the integrator to ramp back toward zero at a rate proportional to the reference voltage. The time required to return to zero is measured by the counter in the digital processor. The phase is terminated when the integrator output crosses zero and the counter contents are transferred to the register, or when the BCD counter reaches 20,000 and the over-range indication is activated. When activated, the over-range indication blanks all but the most significant digit and sign.

Seventeen parallel bits (4-1/2 digits) of information are strobed into the buffer register at the end of the integration phase. Information for each digit is multiplexed out to the BCD outputs (TL503C) or the seven-segment drivers (TL502C) at a rate equal to the oscillator frequency divided by 200.

\*This step is the voltage at pin 2 with respect to analog ground

FIGURE 1. VOLTAGE WAVEFORMS AND TIMING DIAGRAM

NOTES: A. Pin 18 of the TL502C provides an output of  $f_{\rm OSC}$  (oscillator frequency)  $\pm$  20,000. B. The trigger input assumes a high level if not externally connected.

# FIGURE 2. BLOCK DIAGRAM OF BASIC ANALOG-TO-DIGITAL CONVERTER USING TL500 OR TL501 AND TL502C OR TL503C

| MODE      | ANALOG   | COMPARATOR            | CONTROLS<br>A AND B | ANALOG SWITCHES<br>CLOSED |

|-----------|----------|-----------------------|---------------------|---------------------------|

| Auto Zero | >        | C. in the contract of | -                   | 013 03 23 73 63           |

| Hold↑     | <        | Oscillation           |                     | 33, 34, 37, 33, 310       |

| Integrate | Positive | Ι                     | 2                   | 63 63                     |

| Input     | Negative | 7                     |                     | 31, 32                    |

| Integrate | >        | ‡7                    | Η                   | S3, S6, S7                |

| Reference | <        | ‡±                    | ηн                  | 83, 35, 58                |

H ≅ High, L ≡ low, X ≡ Irrelevant

to continue or resume normal operation. ‡ This is the state of the comparator output as determined by the polarity of the analog input during the integrate input phase.

f If the trigger input is low at the beginning of the auto-zero cycle, the system will enter the hold mode. A high level (or open circuit) will signal the digital processor

### description of analog processors

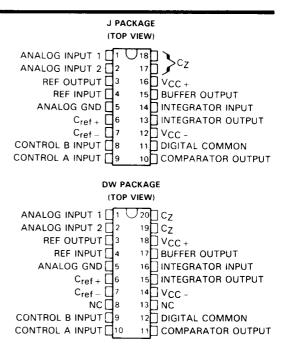

The TL500 and TL501 analog processors are designed to automatically compensate for internal zero offsets, integrate a differential voltage at the analog inputs, integrate a voltage at the reference input in the opposite direction, and provide an indication of zero-voltage crossing. The external control mechanism may be a microcomputer and software routing, discrete logic, or a TL502C or TL503C controller. The TL500 and TL501 are designed primarily for simple, cost-effective, dual-slope analog-todigital converters. Both devices feature true differential analog inputs, high input impedance, and an internal reference-voltage source. The TL500 provides 4-1/2-digit readout accuracy when used with a precision external reference voltage. The TL501 provides 100-ppm linearity error and 3-1/2-digit accuracy capability. These devices are manufactured using TI's advanced technology to produce JFET, MOSFET, and bipolar devices on the same chip. The TL500C and TL501C are characterized for operation over the temperature range of 0°C to 70°C. The TL500I and TL501I are characterized for operation from -40°C to 85°C.

NC - No internal connection

### **AVAILABLE OPTIONS**

|               | LINEARITY | PAC                | KAGE                 |

|---------------|-----------|--------------------|----------------------|

| TA            | ERROR     | CERAMIC DIP<br>(J) | WIDE-BODY SO<br>(DW) |

| 0°C to 70°C   | 0.005% FS | TL500CJ            | TL500CDW             |

| 0-0 10 70-0   | 0.05% FS  | TL501CJ            | TL501CDW             |

| -40°C to 85°C | 0.005% FS | TL500IJ            | TL500IDW             |

| -40-0 10 85-0 | 0.05% FS  | TL501IJ            | TL501IDW             |

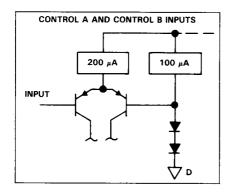

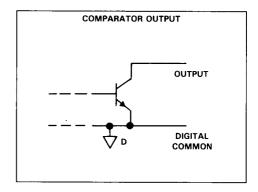

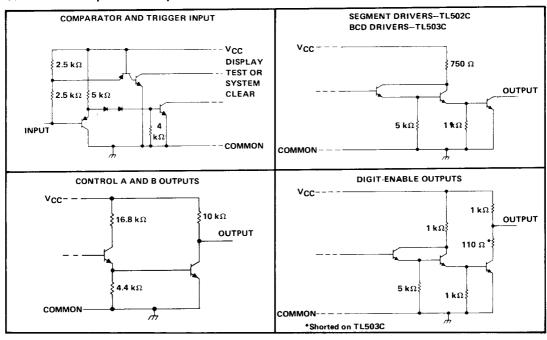

### schematics of inputs and outputs

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Positive supply voltage, VCC+ (see Note 1)                                     |

|--------------------------------------------------------------------------------|

| Negative supply voltage, V <sub>CC</sub>                                       |

| Input voltage, VI ±VCC                                                         |

| Comparator output voltage range (see Note 2)                                   |

| Comparator output sink current (see Note 2)                                    |

| Buffer, reference, or integrator output source current (see Note 2) 10 mA      |

| Total dissipation                                                              |

| Operating free-air temperature range: TL500I, TL501I                           |

| TL500C, TL501C 0°C to 70°C                                                     |

| Storage temperature range                                                      |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds: DW package 260°C |

| Lead temperature 1,6 mm (1/16 inch) from case for 60 seconds: J package        |

NOTES: 1. Voltage values, except differential voltages, are with respect to the analog ground common pin tied together.

2. Buffer, integrator, and comparator outputs are not short-circuit protected.

### DISSIPATION RATING TABLE

| PACKAGE | T <sub>A</sub> ≤ 25°C<br>POWER RATING | DERATING FACTOR ABOVE TA = 25°C | TA = 70°C<br>POWER RATING | TA = 85°C<br>POWER RATING |

|---------|---------------------------------------|---------------------------------|---------------------------|---------------------------|

| DW      | 1125 mW                               | 9 mW/°C                         | 720 mW                    | 585 mW                    |

| J       | 1025 mW                               | 8.2 mW/°C                       | 656 mW                    | 533 mW                    |

### recommended operating conditions

|                                                         |                | MIN    | NOM  | MAX                | UNIT   |

|---------------------------------------------------------|----------------|--------|------|--------------------|--------|

| Positive supply voltage, V <sub>CC+</sub>               |                | 7      | 12   | 15                 | V      |

| Negative supply voltage, V <sub>CC</sub> -              |                | -9     | - 12 | - 15               | V      |

| Reference input voltage, V <sub>ref(I)</sub>            |                | 0.1    |      | 5                  | V      |

| Analog input voltage, V <sub>I</sub>                    |                |        |      | ± 5                | V      |

| Differential analog input voltage, VID                  |                | - 1    |      | 10                 | V      |

| High-level input voltage, VIH                           | Control inputs | 2      |      |                    | l v    |

| Low-level input voltage, VIL                            | Control inputs | •      |      | 0.8                | V      |

| Peak positive integrator output voltage, VON            | +9             |        |      | $\overline{}$      |        |

| Peak negative integrator output voltage, VOM -          |                | - 5    |      |                    | V      |

| Full scale input voltage                                |                |        |      | 2 V <sub>ref</sub> |        |

| Autozero and reference capacitors, Cz and Cref          |                | 0.2    |      |                    | μF     |

| Integrator capacitor, CX                                | -              | 0.2    |      |                    | μF     |

| Integrator resistor, RX                                 |                | 15     |      | 100                | kΩ     |

| Integrator time constant, R <sub>X</sub> C <sub>X</sub> |                | See    |      |                    |        |

|                                                         |                | Note 3 |      |                    |        |

| Free-air operating temperature, TA                      | TL500I, TL501I | -40    |      | 85                 | 0.0    |

| Tree-air operating temperature, 1 A                     | TL500C, TL501C | 0      |      | 70                 | °C     |

| Maximum conversion rate with TL502C or T                | L503C          |        | 3    | 12.5               | conv/s |

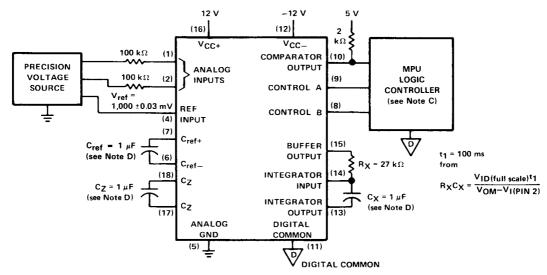

# system electrical characteristics at V<sub>CC $\pm$ </sub> = $\pm$ 12 V, V<sub>ref</sub> = 1,000 $\pm$ 0.03 mV, T<sub>A</sub> = 25 °C (unless otherwise noted) (see Figure 3)

| PARAMETER                                   | TEST COMPLETIONS            | TEST CONDITIONS TL501 |                 |      | TL500 |                 | )     |        |

|---------------------------------------------|-----------------------------|-----------------------|-----------------|------|-------|-----------------|-------|--------|

| TANAMETER                                   | TEST CONDITIONS             | MIN                   | TYP             | MAX  | MIN   | TYP             | MAX   | UNIT   |

| Zero error                                  |                             | Î                     | 50              | 300  |       | 10              | 30    | μV     |

| Linearity error relative to full scale      | V <sub>I</sub> = 2 V to 2 V | Î                     | 0.005           | 0.05 |       | 0.001           | 0.005 | %FS    |

| Full scale temperature coefficient          | T / "                       | 1                     | 6               |      |       | 6               |       | ppm/°C |

| Temperature coefficient of zero error       | $T_A = full range$          |                       | 4               | •    |       | 1               |       | μV/°C  |

| Rollover error <sup>†</sup>                 |                             |                       | 200             | 500  |       | 30              | 100   | μV     |

| Equivalent peak-to-peak input noise voltage |                             |                       | 20              |      |       | 20              |       | μV     |

| Analog input resistance                     | Pin 1 or 2                  | 1                     | 10 <sup>9</sup> |      |       | 10 <sup>9</sup> |       | Ω      |

| Common-mode rejection ratio                 | $V_{IC} = -1 V to +1 V$     | 1                     | 86              |      |       | 90              |       | dB     |

| Current into analog input                   | V <sub>I</sub> = ±5 V       |                       | 50              |      |       | 50              |       | ρA     |

| Supply voltage rejection ratio              |                             | <u> </u>              | 90              |      |       | 90              | -     | dB     |

<sup>†</sup>Rollover error is the voltage difference between the conversion results of the full-scale positive 2 V and the full-scale negative 2 V. NOTE 3. The minimum integrator time constant may be found by use of the following formula:

Minimum

$$R_X C_X = \frac{V_{ID} \text{ (full scale) } t_1}{|V_{OM}| - |V_I(pin 2)}$$

where

V<sub>ID</sub> = voltage at pin with respect to pin 2

$V_{I}(pin 2) = voltage at pin 2 with respect to analog ground$

t<sub>1</sub> = input integration time seconds

# TL500I, TL500C, TL501I, TL501C ANALOG PROCESSORS

### electrical characteristics at $V_{CC\pm} = \pm 12 \text{ V}$ , $V_{ref} = 1 \text{ V}$ , $T_A = 25 \,^{\circ}\text{C}$ (see Figure 3)

### integrator and buffer operational amplifiers

|                  | PARAMETER                     | TEST CONDITIONS                  | MIN | TYP | MAX | UNIT |

|------------------|-------------------------------|----------------------------------|-----|-----|-----|------|

| ٧ı٥              | Input offset voltage          |                                  |     | 15  |     | mV   |

| I <sub>IB</sub>  | Input bias current            |                                  |     | 50  |     | pА   |

| V <sub>OM+</sub> | Positive output voltage swing |                                  | 9   | 11  |     | V    |

| Vom-             | Negative output voltage swing |                                  | - 5 | - 7 |     | V    |

| AVD              | Voltage amplification         |                                  |     | 110 |     | dB   |

| B <sub>1</sub>   | Unity-gain bandwidth          |                                  |     | 3   |     | MHz  |

| CMRR             | Common mode rejection         | $V_{IC} = -1 V \text{ to } +1 V$ |     | 100 |     | dB   |

| SR               | Output slew rate              |                                  | 1   | 5   |     | V/μs |

### comparator

|                 | PARAMETER                 | TEST CONDITIONS          | MIN | TYP | MAX | UNIT |

|-----------------|---------------------------|--------------------------|-----|-----|-----|------|

| V <sub>IO</sub> | Input offset voltage      |                          |     | 15  | •   | mV   |

| Iв              | Input bias current        |                          |     | 50  |     | pΑ   |

| AVD             | Voltage amplification     |                          |     | 100 |     | dB   |

| VOL             | Low-level output voltage  | I <sub>OL</sub> = 1.6 mA |     | 200 | 400 | mV   |

| 10H             | High-level output current | V <sub>OH</sub> = 3 V    |     | 5   | 20  | nΑ   |

### voltage reference output

|                     | PARAMETER                   | TEST CONDITIONS           | MIN  | TYP  | MAX  | UNIT   |

|---------------------|-----------------------------|---------------------------|------|------|------|--------|

| V <sub>ref(0)</sub> | Reference voltage           |                           | 1.12 | 1.22 | 1.32 | V      |

|                     | Reference-voltage           | T                         | - 00 |      |      |        |

| αV <sub>ref</sub>   | temperature coefficient     | $T_A = \text{full range}$ |      | 80   |      | ppm/°C |

| ro                  | Reference output resistance |                           |      | 3    |      | Ω      |

### logic control section

|      | PARAMETER                | TEST CONDITIONS         | MIN | TYP  | MAX   | UNIT |

|------|--------------------------|-------------------------|-----|------|-------|------|

| III- | High-level input current | V <sub>IH</sub> = 2 V   |     | 1    | 10    | μΑ   |

| IIL  | Low-level input current  | V <sub>IL</sub> = 0.8 V |     | - 40 | - 300 | μΑ   |

### total device

|       | PARAMETER               | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-------|-------------------------|-----------------|-----|-----|-----|------|

| Icc+  | Positive supply current |                 |     | 15  | 20  | mA   |

| ICC - | Negative supply current |                 |     | 12  | 18  | mA   |

### PARAMETER MEASUREMENT INFORMATION

NOTES: C. Tests are started approximately 5 seconds after power-on.

D. Capacitors used are TRW's X363UW polypropylene or equivalent for C<sub>X</sub>, C<sub>ref</sub>, and C<sub>Z</sub>; however for C<sub>ref</sub> and C<sub>Z</sub> film-dielectric capacitors may be substituted.

### FIGURE 3. TEST CIRCUIT CONFIGURATION

### external-component selection guide

The autozero capacitor C<sub>Z</sub> and reference capacitor C<sub>ref</sub> should be within the recommended range of operating conditions and should have low-leakage characteristics. Most film-dielectric capacitors and some tantalum capacitors provide acceptable results. Ceramic and aluminum capacitors are not recommended because of their relatively high-leakage characteristics.

The integrator capacitor C<sub>X</sub> should also be within the recommended range and must have good voltage linearity and low dielectric absorption. A polypropylene-dielectric capacitor similar to TRW's X363UW is recommended for 4-1/2-digit accuracy. For 3-1/2-digit applications, polyester, polycarbonate, and other film dielectrics are usually suitable. Ceramic and electrolytic capacitors are not recommended.

Stray coupling from the comparator output to any analog pin (in order of importance 17, 18, 14, 7, 6, 13, 1, 2, 15) must be minimized to avoid oscillations. In addition, all power supply pins should be bypassed at the package, for example, by a 0.01-µF ceramic capacitor.

Analog and digital common are internally isolated and may be at different potentials. Digital common can be within 4 V of positive or negative supply with the logic decode still functioning properly.

The time constant RxCx should be kept as near the minimum value as possible and is given by the formula:

$$Minimum R_X C_X = \frac{V_{ID} (full scale) t_1}{|V_{OM} - | - V_I(pin2)}$$

where:

V<sub>ID</sub>(full scale) = Voltage on pin 1 with respect to pin 2

t<sub>1</sub> = Input integration time in seconds

$V_{I(pin2)}$  = Voltage on pin 2 with respect to analog ground.

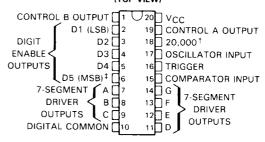

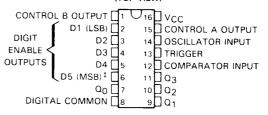

### description of digital processors

The TL502C and TL503C are control logic devices designed to complement the TL500 and TL501 analog processors. They feature interdigit blanking, over-range blanking, an internal oscillator, and a fast display scan rate. The internal-oscillator input is a Schmitt trigger circuit that can be driven by an external clock pulse or provide its own time base with the addition of a capacitor. The typical oscillator frequency is 120 kHz with a 470-pF capacitor connected between the oscillator input and ground.

The TL502C provides seven-segment-display output drivers capable of sinking 100 mA and compatible with popular common-anode displays. The TL503C has four BCD output drivers capable of 100-mA sink currents. The code (see next page and Figure 4) for each digit is multiplexed to the output drivers in phase with a pulse on the appropriate digit-enable line at a digit rate equal to f<sub>OSC</sub>, divided by 200. Each digit-enable output is capable of sinking 20-mA.

The comparator input of each device, in addition to monitoring the output of the zero-crossing detector in the analog processor, may be used in the display test mode to check for wiring and display faults. A high logic level (2 to 6.5 V) at the trigger input with the comparator input at or below 6.5 V starts the integrate-input phase. Voltage levels equal to or greater than 7.9 V on both the trigger and comparator inputs clear the system and set the BCD counter to 20,000. When normal operation resumes, the conversion cycle is restarted at the auto zero phase.

These devices are manufactured using I<sup>2</sup>L and bipolar techniques. The TL502C and TL503C are characterized for operation from 0°C to 70°C.

# TL502C . . . N PACKAGE (TOP VIEW)

# TL503C . . . N PACKAGE (TOP VIEW)

$^{\dagger}\text{Pin}$  18 of TL502C provides an output of  $f_{\text{OSC}}$  (oscillator frequency) + 20,000.

### TABLE OF SPECIAL FUNCTIONS

$V_{CC} = 5 V \pm 10\%$

| TRIGGER<br>INPUT                            | COMPARATOR<br>INPUT   | FUNCTION                                                       |

|---------------------------------------------|-----------------------|----------------------------------------------------------------|

| V <sub>1</sub> ≤0.8 V                       | V <sub>I</sub> ≤6.5 V | Hold at auto-zero cycle after completion of conversion         |

| 2 V≤V <sub>1</sub> ≤6.5 V                   | V <sub>I</sub> ≤6.5 V | Normal operation (continuous conversion)                       |

| V <sub>I</sub> ≤6.5 V V <sub>I</sub> ≥7.9 V |                       | Display Test: All BCD outputs high                             |

| V <sub>I</sub> ≥7.9 V                       | V <sub>1</sub> ≤6.5 V | Internal Test                                                  |

| Both inputs to go V <sub>I</sub> ≥7.9 V     |                       | System clear: Sets BCD counter to 20,000.                      |

| simultaneously                              |                       | When normal operation is resumed, cycle begins with Auto Zero. |

<sup>&</sup>lt;sup>‡</sup>D5, the most significant bit, is also the sign bit.

### DIGIT 5 (MOST SIGNIFICANT DIGIT) CHARACTER CODES

|           |   | TL5 | O2C SE | VEN-SE | SMENT | LINES |   | TL5030 | BCD C      | UTPUT | LINES |

|-----------|---|-----|--------|--------|-------|-------|---|--------|------------|-------|-------|

| CHARACTER |   | В   | C      |        | -     | -     | G | 03     | Q2         | Q1    | QO    |

|           | A | В   | -      | U      | E     | г     | G | 8      | 8 4<br>H L | 2 1   |       |

| +         | Н | Н   | Н      | Н      | L     | L     | L | Н      | L          | Н     | L     |

| + 1       | н | L   | L      | Н      | L     | L     | L | Н      | Н          | н     | L     |

|           | L | Н   | Н      | L      | Н     | Н     | L | Н      | L          | Н     | Н     |

| - 1       | L | L   | L      | L      | н     | н     | L | н      | Н          | Н     | н     |

DIGITS 1 THRU 4 NUMERIC CODE (See Figure 4)

|        |     | TL5 | 02C SE | VEN-SE | SMENT | LINES |   | TL5030 | BCD C | UTPUT                            | LINES |

|--------|-----|-----|--------|--------|-------|-------|---|--------|-------|----------------------------------|-------|

| NUMBER |     | В   | С      | D      | -     |       | G | 03     | Q2    | Q1                               | QO    |

|        | Α . | В   | C      | U      | E     | F     | G | 8      | 4     | Q1<br>2<br>L<br>L<br>H<br>H<br>L | 1     |

| 0      | L   | L   | L      | L      | L     | Ļ     | Н | L      | L     | L                                | L     |

| 1      | н   | L   | L      | н      | н     | н     | Н | L      | L     | L                                | н     |

| 2      | L   | L   | Н      | L      | L     | Н     | L | L      | L     | Н                                | L     |

| 3      | L   | L   | L      | L      | н     | н     | L | L      | L     | Н                                | н     |

| 4      | Н   | L   | L      | Н      | Н     | L     | L | L      | н     | L                                | L     |

| 5      | L   | Н   | L      | L      | н     | L     | L | L      | Н     | Ł                                | Н     |

| 6      | L   | Н   | L      | L      | L     | L     | L | L      | Н     | Н                                | L     |

| 7      | l L | L   | L      | н      | н     | н     | н | L      | Н     | Н                                | н     |

| 8      | L   | L   | L      | L      | L     | L     | L | Н      | L     | L                                | L     |

| 9      | l L | L   | L      | L      | Н     | L     | L | Н      | L     | L                                | н     |

H = high level, L = low level

### schematics of inputs and outputs

### TL502C, TL503C DIGITAL PROCESSORS

### absolute maximum ratings

|                                      | 7                                                                                                            | V                                                                                                                                                                                  |  |  |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Oscillator                           | 5.5                                                                                                          | V                                                                                                                                                                                  |  |  |

| Comparator or Trigger                | 7 5.5 9 120 40 20 1100 0 to 70 -65 to 150 260                                                                |                                                                                                                                                                                    |  |  |

| BCD or Segment drivers               | 120                                                                                                          |                                                                                                                                                                                    |  |  |

| Digit-enable outputs                 | 40                                                                                                           | mA mA                                                                                                                                                                              |  |  |

| Pin 18 (TL502C only)                 | 20                                                                                                           |                                                                                                                                                                                    |  |  |

| perature (see Note 5)                | 1100                                                                                                         | mW                                                                                                                                                                                 |  |  |

| Operating free-air temperature range |                                                                                                              |                                                                                                                                                                                    |  |  |

|                                      | -65 to 150                                                                                                   | °C                                                                                                                                                                                 |  |  |

| seconds                              | 260                                                                                                          | °C                                                                                                                                                                                 |  |  |

|                                      | Comparator or Trigger BCD or Segment drivers Digit-enable outputs Pin 18 (TL502C only) perature (see Note 5) | Comparator or Trigger   9     BCD or Segment drivers   120     Digit-enable outputs   40     Pin 18 (TL502C only)   20     Derature (see Note 5)   1100     O to 70     -65 to 150 |  |  |

NOTES: 4. Voltage values are with respect to the network ground terminal.

5. For operation above 30 °C free-air temperature, derate linearly to 736 mW at 70 °C at the rate of 9.2 mW/°C.

### recommended operating conditions

|                                          |                               | MIN | NOM | MAX | UNIT |

|------------------------------------------|-------------------------------|-----|-----|-----|------|

| Supply voltage, V <sub>CC</sub>          |                               | 4.5 | 5   | 5.5 | V    |

| High-level input voltage, VIH            | Comparator and trigger inputs | 2   |     |     | V    |

| Low-level input voltage, V <sub>IL</sub> | Comparator and trigger inputs |     |     | 0.8 | V    |

| Operating free-air temperature           |                               | 0   |     | 70  | °C   |

electrical characteristics at 25 °C free-air temperature

|                  |                                                 |                      |                           |                          |        | 000   |       |       | 000   |       | Ì    |

|------------------|-------------------------------------------------|----------------------|---------------------------|--------------------------|--------|-------|-------|-------|-------|-------|------|

|                  | PARAMETER                                       | TERMINAL             | TEST CONDITIONS           | TIONS                    | - 1    | Lagra | 1     | - 1   | ٠l    |       | LINO |

| į                |                                                 |                      |                           |                          | Z<br>Z | ΤΥΡ   | MAX   | Z     |       | MAX   |      |

| VIK              | Input clamp voltage                             | All inputs           | $V_{CC} = 4.5 \text{ V},$ | $l_1 = -12  \text{mA}$   |        | -0.8  | -1.5  |       | -0.8  | - 1.5 | >    |

| +<br>            | Positive-going input threshold voltage          | Oscillator           | V <sub>CC</sub> = 5 V     |                          |        | 1.5   |       |       | 1.5   |       | >    |

| - 1 <sub>V</sub> | Negative-going input<br>threshold voltage       | Oscillator           | V <sub>CC</sub> = 5 V     |                          |        | 6.0   |       |       | 6.0   |       | >    |

| VT+ - VT-        | Hysteresis                                      | Oscillator           | VCC = 5 V                 |                          | 0.4    | 9.0   | 0.8   | 0.4   | 9.0   | 0.8   |      |

|                  | Input current at                                |                      |                           |                          |        |       |       |       |       |       |      |

| + <u>+</u>       | positive-going input                            | Oscillator           | $V_{CC} = 5 V$            |                          | 40     | - 94  | - 170 | - 40  | - 94  | - 170 | ħΑ   |

|                  | threshold voltage                               |                      |                           |                          |        |       |       |       |       |       |      |

|                  | Input current at                                |                      |                           |                          |        |       |       |       |       |       |      |

| <u> </u>         | negative-going input                            | Oscillator           | VCC = 5 V                 |                          | 40     | 117   | 170   | 40    | 117   | 170   | Ψ    |

|                  | threshold voltage                               |                      |                           |                          |        |       |       |       |       |       |      |

|                  |                                                 | Digit enable         |                           |                          | 4.15   | 4 4   |       | 4.15  | 4.4   |       | ;    |

| ло <sub>л</sub>  | High-level output voltage                       | Pin 18 (TL502C only) | $V_{CC} = 4.5 \text{ V},$ | 0 = HO <sub>1</sub>      | 4.25   | 4.4   |       |       |       |       | >    |

|                  |                                                 | Control A and B      |                           |                          | 4.25   | 4.4   |       | 4.25  | 4.4   |       |      |

|                  |                                                 | Digit enable         |                           | I <sub>OL</sub> = 20 mA  |        |       |       |       | 0.2   | 0.5   |      |

|                  |                                                 | Pin 18 (TL502C only) |                           | 10L = 10 mA              |        | 0.15  | 0.4   |       |       |       |      |

| NO <sub>1</sub>  | Low-fevel output voltage                        | Control A and B      | $V_{CC} = 4.5 \text{ V}$  | 10L = 2 mA               |        | 0.088 | 0.4   | 0     | 0.088 | 0.4   | >    |

| }                |                                                 | Segment drivers      |                           | 10L = 100 mA             |        | 0.17  | 0.3   |       |       |       |      |

|                  |                                                 | BCD drivers          |                           | 10L = 100 mA             |        |       |       |       | 0.17  | 0.3   |      |

|                  |                                                 | Comparator, Trigger  |                           |                          |        | 65    | 100   |       | 65    | 100   | Pη   |

| <u>=</u>         | Input current                                   | Oscillator           | , cc = 22v                | > c.c =   >              |        |       | -     |       |       | 1     | Α    |

| -                |                                                 | Comparator, Trigger  | u                         |                          |        | 9.0-  | - 1   |       | -0.6  | - 1   | 8    |

| <u>=</u>         | High-level input current                        | Oscillator           | , v e.e = 22v             | v   = 2.4 v              |        |       | 0.5   |       |       | 0.5   | =    |

|                  |                                                 | Oscillator           | ٠                         |                          |        | - 0.1 | -0.17 |       | -0.1  | -0.17 | Φω   |

| <u>=</u>         | Low-level input voltage                         | Comparator, Trigger  | , v c.c = 22 v,           | v = 0.4 v                |        | -1    | - 1.6 |       | -     | - 1.6 | [    |

|                  |                                                 | Digit enable         |                           | $V_{Q} = 0.5 \text{ V},$ | -2.5   | -4    |       | -2.5  | -4    |       |      |

|                  |                                                 | Pin 18 (TL502C only) |                           | $V_0 = 0.5 V$            | -0.5   | -0.9  |       | ļ     |       |       |      |

| HO!              | High-level output current                       | Control A and B      | $V_{CC} = 4.5 V$          | $V_0 = 0.5 \text{ V}$    | -0.25  | -0.4  |       | -0.25 | -0.4  |       | Ψ    |

|                  | (Output transistor or)                          | Segment drivers      |                           | $V_0 = 5.5 \text{ V}$    |        |       | 0.25  |       |       |       |      |

|                  |                                                 | BCD drivers          |                           | V <sub>0</sub> = 5.5 V   |        |       |       |       |       | 0.25  |      |

| 101              | Low-level output current (Output transistor on) | Digit enable         | VCC = 4.5 V,              | V <sub>0</sub> = 3.55 V  | 18     | 23    |       |       |       |       | mA   |

| 221              | Supply current                                  | 22/                  | V <sub>CC</sub> = 5.5 V   |                          |        | 73    | 110   |       | 73    | 110   | Ą    |

|                  |                                                 |                      |                           |                          |        |       |       |       |       |       |      |

## special functions † operating characteristics at 25 °C free-air temperature

|     | PARAMETER                    | TEST CONDITIONS                                         | MIN | TYP | MAX | UNIT |

|-----|------------------------------|---------------------------------------------------------|-----|-----|-----|------|

| l , | Input current into           | $V_{CC} = 5.5 \text{ V}, \qquad V_{I} = 8.55 \text{ V}$ |     | 1.2 | 1.8 | mA   |

| L'. | comparator or trigger inputs | $V_{CC} = 5.5 \text{ V},  V_{I} = 6.25 \text{ V}$       |     |     | 0.5 | mA   |

<sup>&</sup>lt;sup>†</sup>The comparator and trigger inputs may be used in the normal mode or to perform special functions. See the Table of Special Functions.

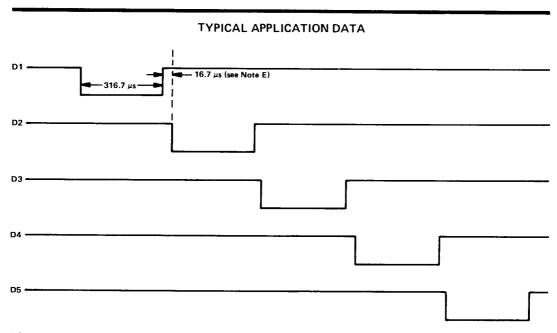

NOTE E: The BCD or seven-segment driver outputs are present for a particular digit slightly before the falling edge of that digit enable.

FIGURE 4. TL502C, TL503C DIGIT TIMING WITH 120-kHz CLOCK SIGNAL AT OSCILLATOR INPUT

# This datasheet has been downloaded from:

www. Data sheet Catalog.com

Datasheets for electronic components.