# Very Wide Input Voltage Range, Off-Line Flyback Switching Power Supply

Prepared by: Marty Brown

http://onsemi.com

# **APPLICATION NOTE**

One of the many problems besetting the power supply designer today is being able to design a switching power supply that is able to operate in all the power systems within their international marketplaces. Forward-mode switching power supplies typically operate over a single power system's range of voltage, that is, 90 to 130 VAC or 200 to 270 VAC. Boost-mode converters can just make the range of 90 to 270 VAC. Any higher input voltages would then require a different design.

This leads companies to create products targeted at specific marketplaces, which can be costly, or to have their customers arrange jumpers to accommodate their power system which can be annoying or lead to costly errors.

Added to this are those industrial companies which may not only have their products reside on residential power systems but also have the varied international industrial power systems. This means that a single product family might have to operate from an input voltage of 90 to 600 VAC, well beyond the residential limits of 90 to 270 VAC.

This paper reviews one method of enabling a discontinuous-mode flyback converter to operate beyond its traditional range of input voltage of 3:1 to a range of more than 6.6:1 without affecting the reliability of its operation. This is done by changing its mode of operation and the use of recently available power MOSFETs with breakdown voltage ratings of 1,200 V.

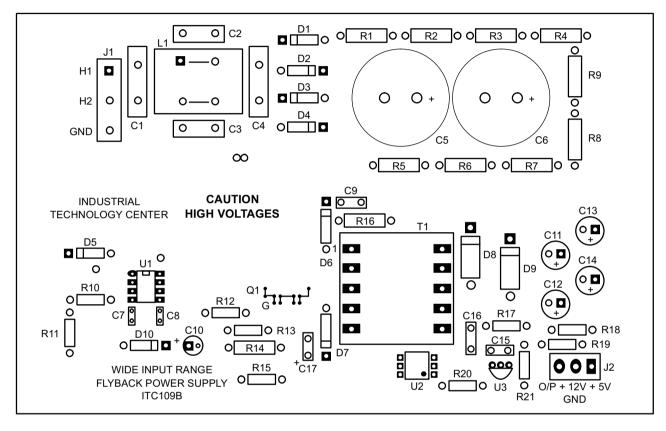

Figure 1. The Wide Input Range Flyback Power Supply Demonstration Board

This document may contain references to devices which are no longer offered. Please contact your ON Semiconductor representative for information on possible replacement devices.

# A Summary of the Operation of Fixed Frequency Flyback Converters

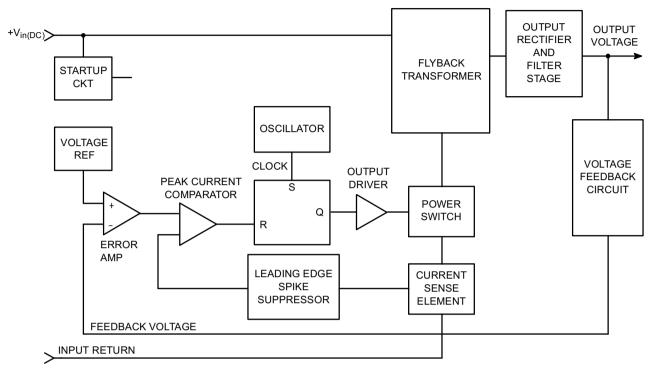

The most common topology for those applications less than 150 W has been the fixed frequency, current-mode

controlled, flyback converter. Its block diagram can be seen in Figure 2.

Figure 2. Block Diagram of a Fixed Frequency Current-Mode, Flyback Converter

Here a fixed frequency oscillator initiates a power switch conduction period which is terminated by either the current within the power switch reaching a predetermined limit as set by the error amplifier or the oscillator terminating the period and initiating the next power switch conduction period.

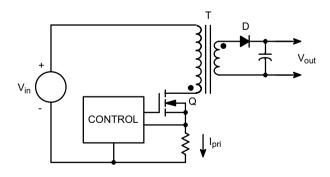

A representative flyback converter can be seen in Figure 3.

Figure 3. A Simplified Schematic of a Flyback Converter

The power switch essentially places the primary inductance of the flyback transformer across the input voltage source when it is turned on. The secondary is disconnected because the output rectifier (D) is reverse biased. The primary winding's current takes the form of a linear ramp starting from zero amps and whose peak value is given by:

$$i_{pk} = \frac{V_{in} \cdot T_{on}}{L_{pri}}$$

(eq. 1)

The slope of the current ramp is  $V_{in}/L_{pri}$ .

The flyback topology, as with all boost-mode converters, operate under the principle of storing energy within the core material of the transformer. The energy stored during each conduction period is given by:

$$\mathsf{E}_{\mathsf{Sto}} = \frac{\mathsf{L}_{\mathsf{pri}} \cdot \mathsf{i} \, \frac{2}{\mathsf{pk}}}{2} \tag{eq. 2}$$

To meet the short-term steady-state power demands of the load(s), the following relationship must be met:

$$P_{out} \le \frac{f_{op} \cdot L_{pri} \cdot i \frac{2}{pk}}{2}$$

(eq. 3)

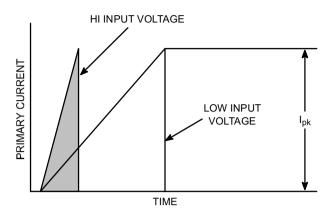

In reality, for any one output power, the current-mode controller strives to maintain a constant value for  $I_{pk}$  over the entire range of input voltages as visualized in Figure 4.

Figure 4. Peak Currents at Differing Input Voltages

The shortcoming arises in the output drivers of the typical current-mode control IC and the power switch. Typically a

power MOSFET is used as the power switch in most modern flyback power supplies. At high input voltages, the on-time of the power switch becomes so short (300 - 600 nS) that the output driver cannot source enough instantaneous current to drive the MOSFET into a saturated condition before turning it back off. The effect is the power switch operates in the linear conduction mode during these short "on" pulses. This causes a drastic drop in power switch operating efficiency and jeopardizes the power supply's reliability.

#### The New Method of Control

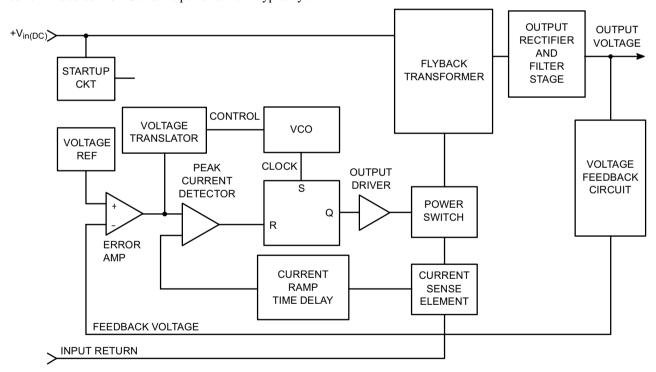

By a very simple modification to the traditional fixed frequency current-mode controlled flyback converter design, one can greatly extend its operational input voltage range. The modifications make the control method one of variable on-time, and variable frequency. Figure 5 illustrates the newly added and redefined functional blocks of this new method of control.

Figure 5. Block Diagram of the Wide Input Range, Flyback Converter

A VCO (voltage-controlled oscillator) is created by removing the timing capacitor's charging circuit from a fixed voltage or current source and placing it under the control of the error voltage. In the design example shown later, it means simply removing the timing resistor from the voltage reference and wiring it to a variable voltage created by the output of the error amplifier. A voltage translator is placed between the output of the error amplifier and the control input to the VCO. It consists of a simple biased 3.3 V zener diode so that the error amplifier may make use of its

entire output voltage swing. The other new block is really a redefinition of an old familiar function - the leading edge spike filter from the current sensing element. Here, the formerly annoying parasitic of time lag serves an important function within the control algorithm. It now delays the actual current ramp prior to being sensed by the control IC. It allows the actual peak current to increase with increasing input voltages while the controller sees a lowering peak current needed by this control strategy. This will be discussed later.

The ultimate goal of the new control methodology is to force the on-time of the power switch to be greater than this minimum effective on-time over the power supply's entire line/load operating range. Its operation can be best understood by examining equation 3. The error amplifier/VCO section of the circuit lowers the operating frequency as the input voltage is increased. This requires the energy stored per conduction period to increase to meet the short-term power requirement of the output. This is done by extending the on-time of the power switch. If the key component parameters such as maximum operating flux density ( $B_{max}$ ) of the transformer, the avalanche ratings of the diodes and power switch, and the current ratings of the output rectifiers are adequate, then no degradation in the reliable operation of the supply is experienced.

Its operation can be better defined by rearranging equation 3 and neglecting any power loss due to the inefficiency of the supply one gets:

$$i_{pk} = \sqrt{\frac{2 \, P_{out}}{L_{pri} \cdot f(f(Ve))}} \tag{eq. 4}$$

where f(f(Ve)) is the controlled frequency of the power supply.

As one can see, the peak current is inversely proportional to the square root of the frequency of operation, since all the other terms are fixed in the short-term operation and by the circuit design.

By substituting equation 1 into equation 4 one further gets:

$$t_{on} = \frac{1}{V_{in}} \cdot \sqrt{\frac{2 P_{out} \cdot L_{pri}}{f(f(Ve))}}$$

(eq. 5)

There are more unknowns than there are independent equations, but at the low input line voltage and at the rated output load, one can solve equation 5. The input voltage is known to be 125 VDC (90 VAC), the frequency will be at its highest point as designated by the designer, the on-time will be one-half of the entire operating period and the peak current will be calculated as it is in a common

fixed-frequency flyback converter. This will allow us to determine the appropriate value for the primary inductance.

In the sample design, the frequency of operation at the highest input voltage will drop to one-half from that at the lowest input voltage. Equation 4 then dictates:

$$ipk(hi) \approx \sqrt{2} ipk(lo)$$

(eq. 6)

If the desired maximum operating flux density (B<sub>max</sub>) is one-half the core material's saturation flux density at 100°C and at the high input line, then the operating flux density at the low input voltage should be:

$$B_{\text{max}(lo)} \approx \frac{B_{\text{Sat}(\text{min})}}{2\sqrt{2}}$$

(eq. 7)

For most common ferrite materials such as 3C8, N27, or F, the operating flux density at low line will be at approximately 1,300 gauss. The  $B_{max}$  at the high input voltage will be no more than one-half the saturation flux density at  $100^{\circ}$ C.

The inductance can now be calculated by using equation 1 at the low input voltage, and an air gap calculated using any one of the common methods.

It is important to determine the secondary inductance such that the core's energy can be emptied as close to 50 percent duty-cycle  $(1/f_{op}(hi))$  as possible. This will minimize the RMS currents to their lowest possible point over the entire operating range. The output peak current at any operating point is described as:

$$i_{pk(out)} \approx 2 \cdot I_{out(av)} \cdot T_{disch} \cdot f_{op}$$

(eq. 8)

This would describe both the peak currents flowing through the output rectifiers and the peak ripple currents flowing into and out of the output filter capacitors. Within the sample design with one ampere rated outputs, at low line the peak-to-peak rectifier currents would be four times the average output current. At the high line, the peak-to-peak currents would be eight times the average output current for the rated output current.

# The Wide-Range Flyback Converter Demonstration Board

The wide-input range off-line flyback converter described has the following maximum and performance ratings.

Output Power: 17 Watts

Outputs: +5.0 Vdc @ 1.0 Amp Max

+12 Vdc @ 1.0 Amp Max

Input Voltage Range: 90 V<sub>RMS</sub> - 600 V<sub>RMS</sub>

Maximum Input Voltage: 675 V<sub>RMS</sub>

Figure 6. Printed Circuit Board Layout

Table 1. Parts List

| Designator | Quantity | Value/Rating      | Description             |

|------------|----------|-------------------|-------------------------|

| C1, C4     | 2        | 0.1 μF, 1.0 kV    | Capacitor, Ceramic      |

| C2, C3     | 2        | 0.0047 μF, 3.0 kV | Capacitor, Ceramic      |

| C5, C6     | 2        | 100 μF, 450 V     | Capacitor, Electrolytic |

| C7         | 1        | 220 pF, 50 V      | Capacitor, Ceramic      |

| C8         | 1        | 1000 pF, 50 kV    | Capacitor, Ceramic      |

| C9         | 1        | 1000 pF, 1.0 kV   | Capacitor, Ceramic      |

| C10        | 1        | 10 μF, 25 V       | Capacitor, Tantalum     |

| C11, C12   | 2        | 100 μF, 20 V      | Capacitor, Tantalum     |

| C13, 14    | 2        | 100 μF, 10 V      | Capacitor, Tantalum     |

| C15        | 1        | 1500 pF, 50 V     | Capacitor, Ceramic      |

| C16        | 1        | 1.3 μF, 50 V      | Capacitor, Mylar        |

| C17        | 1        | 0.22 μF, 35 V     | Capacitor, Ceramic      |

| D1-D4      | 4        | 1.0 A, 1.0 kV     | Diode, 1N4007           |

| D5         | 1        | 3.3 V, 500 mW     | Zener Diode, 1N5226B    |

| D6         | 1        | 1.0 A, 1.0 kV     | Diode, UF, MUR1100E     |

| D7         | 1        | 4.0 A, 300 V      | Diode, UF, MUR430E      |

| D8         | 1        | 3.0 A, 70 V       | Diode, Schottky, MBR370 |

| D9         | 1        | 1.0 A, 300 V      | Diode, UF, MUR130E      |

| D10        | 1        | -                 | Diode, SIGNAL, 1N4148   |

| J1         | 1        | -                 | Connector               |

| J2         | 1        | -                 | Connector               |

| L1         | 1        | -                 | Coil Craft P/N E3493    |

| Q1         | 1        | 3.0 A, 1.2 kV     | MOSFET, MTB3N120E       |

| R1-R4      | 4        | 470 kΩ, 1/2 W     | Resistor                |

| R5-R9      | 5        | 82 kΩ, 1/2 W      | Resistor                |

| R10        | 1        | 1.8 kΩ, 1/4 W     | Resistor                |

| R11        | 1        | 27 kΩ, 1/4 W      | Resistor                |

| R12        | 1        | 10 Ω, 1/4 W       | Resistor                |

| R13        | 1        | 1.0 kΩ, 1/4 W     | Resistor                |

| R14        | 1        | 1.2 Ω, 1/2 W      | Resistor                |

| R15        | 1        | 680 Ω, 1/4 W      | Resistor                |

| R16        | 1        | 100 kΩ, 1/2 W     | Resistor                |

| R17        | 1        | 7.5 kΩ, 1/4 W     | Resistor                |

| R18        | 1        | 3.57 kΩ, 1/4 W    | Resistor                |

| R19        | 1        | 32.4 kΩ, 1/4 W    | Resistor                |

| R20        | 1        | 120 Ω, 1/4 W      | Resistor                |

| R21        | 1        | 2.49 kΩ, 1/4 W    | Resistor                |

| T1         | 1        | Transformer       | Cramer, CSM, 3015-027   |

| U1         | 1        | -                 | IC, UC3845B             |

| U2         | 1        | -                 | Optoisolator, MOC8102   |

| U3         | 1        | -                 | IC, TL431CLP            |

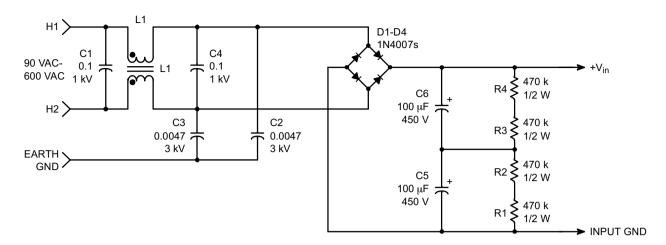

Figure 7. AC Input/Filter Circuit Section

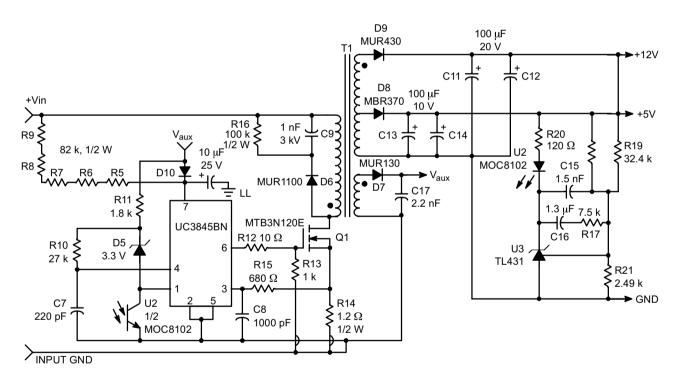

Figure 8. DC/DC Converter Circuit Section

# Design of the Wide Input Range Flyback Converter

#### **Predesign Considerations**

Output Power:

$$P_0 = (5.0 \text{ V})(1.0 \text{ A}) + (12 \text{ V})(1.0 \text{ A}) = 17 \text{ Watts}$$

DC Input Voltages:

$$\begin{array}{ll} V_{in(low)} &= 1.414 \cdot V_{in\text{-}ac(low)} \\ &= 1.414(90 \text{ VAC}) = 127 \text{ VDC} \\ V_{in(hi)} &= 1.414 \cdot V_{in(hi)} \\ &= 1.414(600 \text{ VAC}) = 854 \text{ VDC} \end{array}$$

Maximum Average Input:

Current:

$$I_{\text{in-av(max)}} = P_{\text{out}}/(\text{eff} \cdot V_{\text{in(min)}})$$

= (17 W)/(0.8)(127 VDC)

= 167 mA

NOTE: The primary winding's AWG should be #30 AWG.

Nominal Peak Current:

$$\begin{split} I_{pk} & = 5.5 \cdot P_{out} / V_{in(min)} \\ & = 5.5 (17 \text{ W}) / 127 \text{ V} = 0.74 \text{ Amps} \end{split}$$

The desired maximum frequency of operation is 140 kHz.

#### **Designing the Transformer**

After reviewing the core sizing information provided by the various core manufacturers, it is decided that an E-E core of about 1.2 inches (30.5 mm) on a side will adequately fit the windings and insulation needed by this application. This corresponds to a Magnetics Inc. part number 43007-EC core (or Philips 782E272 (E 30)). The core material should be a Magnetics P, F or N material or Philips 3C85 or 3F3 material. A Magnetics part number F-43007-EC will be used.

Calculating the primary inductance needed for this application:

$$\begin{aligned} \mathsf{L}_{\text{pri}} &= \frac{\partial \max \ \mathsf{Vin}(\mathsf{min})}{\mathsf{Ipkf} \max} \\ &= \frac{0.5(127 \ \mathsf{V})}{(0.82 \ \mathsf{A})(140 \ \mathsf{kHz})} = 553 \ \mu\mathsf{H} \end{aligned} \tag{eq. 9}$$

Using equation 6, one gets the maximum operating flux density at the low input voltage of:

$$B_{\text{max}(lo)} \approx \frac{3500 \text{ G}}{2\sqrt{2}} = 1237 \text{ G}$$

(eq. 10)

The minimum length of the airgap for the core is then:

$$I_{g} = \frac{0.4 \pi L_{pri} i_{pk}^{2} 10^{8}}{A_{C}B_{max}^{2}}$$

(eq. 11)

$$= \frac{0.4 \ \pi \ (553 \ \mu H)(0.82 \ A)^2 \ 10^8}{(0.6 \ cm^2)(1300 \ G)^2} = 0.046 \ cm \ or \ 18 \ mils$$

An airgap that produces an  $A_L$  of 100 mH/1000T is larger than this, so that is what is used.

The number of turns needed to produce the required primary inductance is:

$$\begin{split} N_{pri} &= 1000 \, \sqrt{\frac{L_{pri}}{A_L}} \\ &= 1000 \, \sqrt{\frac{0.553 \; mH}{100 \; mH}} = 74.4 \; turns, \; make \; 74 \; turns \end{split}$$

The number of turns needed by the +12 V secondary, and assuming ultrafast recovery rectifier is:

$$\begin{split} \text{N}_{\,\text{SeC}} &= \frac{(\text{V}_{\text{out}} \ + \ \text{V}_{\text{fwd}})(1 - \partial_{\,\text{max}}) \cdot \text{N}_{\text{pri}}}{\partial_{\,\text{max}} \cdot \text{Vin(min)}} \\ &= \frac{(12 \ \text{V} + 0.9 \ \text{V})(0.5)(74 \ \text{T})}{(0.5)(127 \ \text{VDC})} = 7.5 \ \text{turns, make 8 turns} \end{split}$$

The auxiliary winding to power the control IC is also +12 V, so it will have the same number of turns.

The number of turns needed for the +5.0 volt winding is:

$$N_{(+5)} = \frac{(5 V + 0.5 V)(8T)}{(12.9 V)} = 4 turns$$

(eq. 14)

The amount of error between the actual transformer output voltages and the required output voltages are:

Add one turn (9 turns) to the +12 V outputs. The resulting output voltage, including the rectifier drop is 11.5 volts.

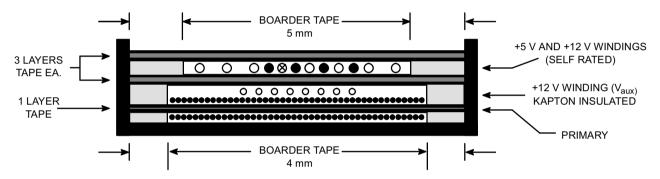

The physical winding of the transformer is extremely important (refer to Figure 9). First, there are the creepage requirements (space between windings over surface) of the safety agencies. Secondly, with 850 volts across the primary winding at the high input voltage, the interlayer voltage could cause arcing between layers of the primary winding. A layer of Mylar tape must be placed between adjacent layers of the primary. The final transformer construction is given below.

## Sizing the Output Filter Capacitors

Since this is a variable frequency system, all the calculations for the value of the output filter capacitors will be done at the lowest frequency since the ripple voltage will be greatest at this frequency. Since capacitor values are determined by the output current, and both the +5.0 V and the +12 V outputs have the same maximum output current rating, their capacitance values will be equal.

$$\begin{split} C_{O} &\approx \frac{\text{lo(max)}}{\text{fest(min)} \cdot \text{Vripple(max)}} \\ &\approx \frac{\text{(1 A)}}{\text{(70 kHz)(0.1 V)}} = 142 \, \mu\text{F} \end{split}$$

Make the output capacitors two  $100 \,\mu\text{F}$  capacitors placed in parallel for each output (C11 and C13, C13 and C14).

# **Designing the Voltage Feedback Section**

The internal error amplifier in the UC3845 (U1) will not be used. The inverting input pin should be grounded to ensure that the output will be always high. The error amplifier function will be provided by a TL431 (U3) on the secondary being connected to the primary side via an optoisolator, the MOC8102 (U2).

The collector of the MOC8102 optoisolator represents the key control node for power supply. The value of the voltage at this node sets both the frequency of operation and the peak current flowing through the power switch during each cycle. The collector of the U2 will be connected to the compensation pin of the UC3845 which will directly set the peak current. Then a 3.3 volt zener diode (D5) will elevate this voltage to a higher voltage to set the frequency of the voltage controlled oscillator. Choosing the maximum

current from the output of the MOC8102 optoisolator to be 5.0 mA, an external resistor (R11) from the  $V_{CC}$  of the IC to the VCO input is needed. Its value is set when the MOC8102's output is at saturation and is:

R11 =

$$(12 V - 3.3 V)/5 \text{ mA} = 1740 \text{ ohms, make } 1.8 \text{ k}$$

(eq. 16)

The MOC8102 has a  $C_{\rm trr}$  of 100 percent. That makes the LED current 6.0 mA (5.0 mA from R10, 1.0 mA from pin 1 of U1). A margin of 30 percent should be added for variations in the gain of the optoisolator. That would make the LED current 8.0 mA.

The value of the current limiting resistor for the optoisolator LED (R20) is:

R20 =

$$[5 \text{ V} - (\text{VU3} + \text{VLED})]/8 \text{ mA}$$

= 138 ohms. make 120 k

Figure 9. Construction of the Transformer

The lower resistor of the voltage sensing network (R21) is set by assuming a sense current. One milliamp yields 1.0 k ohm per volt, which is easy. So:

$$R21 = V_{ref}/I_{sense} = 2.5 \text{ V/1 mA}$$

= 2.5 k make 2.49 k 1% (eq. 18)

Splitting the output voltage sensing between more than one output will improve the cross regulation of all the outputs. The +5.0~V output is usually connected to MCUs which are voltage sensitive. Usually, the loads connected to the +12~V output are less susceptible to voltage variations. Select the proportion of sense current to be 70 percent from the +5.0~V and 30 percent from the +12~V outputs. The value of the +5.0~V sense resistor (R18) is:

R18 =

$$\frac{(5 \text{ V} - 2.5 \text{ V})}{0.7(1 \text{ mA})}$$

= 3.57 k, 1% (eq. 19)

The +12 V sense resistor (R19) is:

R19 =

$$\frac{(12.2 \text{ V} - 2.5 \text{ V})}{0.3(1 \text{ mA})}$$

= 32.3 k (eq. 20) make it 32.4 k, 1%

# **Designing the Voltage Controlled Oscillator**

One designs the VCO component values when the power supply is at the lowest input voltage. Here the frequency will

be at its highest and the duty cycle will be 50 percent. The VCO control node will be at its highest linear value which is 7.7 volts.

One starts by selecting the size of the timing capacitor ( $C_t$ , C7). This is done by referring to UC3845 data sheet, Figure 2 "deadtime vs. frequency." It is desired that the deadtime be a minimum, since the UC3845 is already 50 percent duty cycle limited. At an oscillator frequency of 280 kHz, which is divided by 2 for an operating frequency of 140 kHz, the largest capacitor that yields the least deadtime is approximately 220 pF.

Using Figure 1 from the UC3845 data sheet "Timing Resistor vs. Oscillator Frequency" and knowing the VCO control voltage will be 2.2 V higher than the +5.0 V reference assumed by the chart, one can "scale" Figure 1 so that the same charging current is flowing through the timing resistor (R10) but from the higher voltage source. So by multiplying the ratio of 7.7 V divided by 5.0 V by the value of the resultant resistor value from Figure 1, one gets the approximate final resistor value. Figure 1 results in a value of 18 k ohms for the timing resistor for a timing capacitor of 220 pF. The final value of R10 is then:

$$R_t = \frac{7.7 \text{ V } (18 \text{ k})}{5.0 \text{ V}} = 27.7 \text{ k make } 27 \text{ k} \quad \text{(eq. 21)}$$

The lowest frequency that the power supply is capable occurs when the error amplifier is at its lowest output which is about 0.8 V. The lowest operating frequency would then be:

$$f_{low} = \frac{(0.8 \text{ V} + 3.3 \text{ V})}{7.7 \text{ V}} \cdot 140 \text{ kHz} = 75 \text{ kHz} \text{ (eq. 22)}$$

#### The Current Sense Resistor

Determining the value of the current sense resistor (R14), one uses the peak current determined in the predesign considerations and at the minimum input voltage. To keep the current-mode operation linear, the peak currents must be kept less than 1.0 volt in normal operation. So to find the current sensing resistor (R14) value:

$$R_{SC} = \frac{V_{SC}}{I_{pk}} = \frac{1.0 \text{ V}}{0.74 \text{ A}} = 1.35 \Omega \text{ make } 1.2 \text{ ohms, } 1/2 \text{ W}$$

(eq. 23)

#### The Current Ramp Time Delay Circuit

This circuit is very important to the operation of the overall circuit. Aside from providing the usual spike elimination to the current comparator, it also provides a time delay function from the current sense resistor to the input to the current comparator. Although a wide range of resistor and capacitor values will work, some minimum time delay is required to avoid instabilities due to too short an on-time at the high range of input voltages.

One starts by selecting a value for the capacitor (C8). The common range of values for this function are 470 pF to 1000 pF. For this particular application a value of 1,000 pF was selected for C8. A good estimate of the time delay needed would be approximately 0.7  $\mu$ S. This is also the approximate minimum on-time at the high input voltage. The value of the resistor (R15) would then be:

$$R_f = \frac{T_d}{C_f}$$

=  $\frac{(700 \text{ nS})}{(1000 \text{ pF})} = 700 \Omega \text{ make 680 ohms}$  (eq. 24)

# The Start-Up Circuit

A passive start-up circuit is used. That is, resistors will bring current from the input line to start-up the control IC. It is desired that a "hiccup" mode of overcurrent protection be implemented, which means that the amount of current that flows through the start-up circuit must be less than the current needed to run the control IC. The UC3845B uses approximately 10 mA during normal operation and draws between 0.3 to 0.5 mA in standby. The start-up energy will be stored in the 10 µF filter capacitor.

To meet the breakdown rating of the half watt resistors (approximately 250 V), a minimum of four resistors in series will be needed to accommodate the 854 VDC maximum input voltage. The total start-up resistance will be:

$$R_{St} = \frac{V_{in}(min)}{I_{start}(min)} = \frac{127 \text{ V}}{0.3 \text{ mA}} = 423 \text{ k}$$

(eq. 25)

Each resistor is then 110 k

The power dissipated is:

$$P_D = \frac{(Vin(max))^2}{R_{St}} = \frac{(854)^2}{4(110 \text{ k})} = 1.66 \text{ W} \text{ (eq. 26)}$$

This makes the power dissipated in each resistor 0.41 watts. This is a little high, so place five resistors (R5-R9) each having a value of 82 k ohms and each will dissipate 0.36 watts which is below a 25 percent derating point.

#### The Voltage Feedback Loop Compensation

The output that is most heavily sensed is the +5.0 V output, so that will be the output that is used as the reference input for the feedback loop analysis.

The output filter pole at light load (0.1 A) of this output is:

$$\begin{split} f_{fp(+5)} &= \frac{1}{2\pi R_0 C_0} \\ &= \frac{1}{2\pi (50~\Omega) (200~\mu F)} = 15.9~\text{Hz} \end{split} \label{eq:fp(+5)}$$

The +5.0~V output filter pole at rated load (1.0 A) is 159~Hz.

The zero contributed by the ESR of the output filter capacitors will be approximately 15 kHz.

The gain exhibited by the open loop power supply at the high input voltage will be:

$$\begin{split} A_{DC} &= \frac{(V_{in} - V_{out})^2 \, N_{\, sec}}{V_{in} \cdot V_e \cdot N_{pri}} \\ &= \frac{(854 \, V - 5 \, V)^2 \, 4T}{(854 \, V)(1)(70T)} = 48.3 \end{split}$$

(eq. 28)

or  $G_{DC}$  = 33.6 dB. This is the highest DC gain that will be exhibited by the open loop power supply and will reduce to 16.5 dB at the low input line. This will reduce the bandwidth of the closed loop power supply by almost a decade when going from high input line to low input line. This is marginally acceptable. By setting the widest allowable bandwidth at the high input line, then one can be assured of a reasonable bandwidth at the low input line. The maximum recommended bandwidth is approximately:

$$f_{XO} = \frac{f_{SW(min)}}{5} = \frac{75 \text{ kHz}}{5} = 15 \text{ kHz}$$

(eq. 29)

The gain needed to be contributed by the error amplifier to achieve this bandwidth is calculated at rated load because that will yield the widest bandwidth condition which is:

$$G_{XO} = 20 \text{ Log} \left( \frac{f_{XO}}{f_{fp}} \right) - G_{DC}$$

(eq. 30)

$G_{XO} = 20 \text{ Log} \left( \frac{15 \text{ kHz}}{159 \text{ Hz}} \right) - 33.6 \text{ dB} = 5.9 \text{ dB}$

The gain in absolute terms (needed later) is:

$$A_{XO} = 10 \left(\frac{G_{XO}}{20}\right)$$

(eq. 31)

$A_{XO} = 10(5.9 \text{ dB}/20) = 1.97$

Now the compensating circuit elements can be calculated.

$$C15 = \frac{1}{2 \cdot \pi \cdot A_{XO} \cdot R19 \cdot f_{XO}}$$

$$= \frac{1}{2 \cdot \pi (1.97)(3.57 \text{ k})(15 \text{ kHz})}$$

$$= 1500 \text{ pF}$$

$$R17 = A_{XO} \cdot R18$$

$$= (1.97)(3.57 \text{ k}) = 7033 \text{ ohms, make R20 7.5 k}$$

The compensating zero must be placed at or below the light load filter pole.

C16 =

$$\frac{1}{2 \cdot \pi \cdot R20 \cdot f_{Ze}}$$

=  $\frac{1}{2 \cdot \pi (7.5 \text{ k})(15.9 \text{ Hz})} = 1.3 \,\mu\text{F}$  (eq. 33)

# Design of the Input Rectifier/Filter Circuit

This circuit provides EMI filtering, rectification and bulk energy storage for the power supply. It has some severe operating conditions it must withstand, such as very high AC and DC voltages at the high input voltage range. High voltage ratings for the rectifiers and bulk filter capacitors are needed. Also large creepage distances, the distance an arc must travel over a surface, must be maintained to meet the requirements of the safety regulatory agencies.

1N4007's will be used as the input rectifiers because of their 1000 V reverse voltage ratings and the average input current of the power supply is less than 1.0 amp.

# The Bulk Input Filter Capacitor

The approximate value of capacitance needed is:

$$\begin{split} C_{in} &\approx \frac{T_{off} \cdot l_{in} - av(max)}{V_{ripple}} \\ &\approx \frac{(5 \text{ mS})(0.167 \text{ A})}{20 \text{ V}} = 42 \, \mu\text{F} \end{split}$$

make this two 100  $\mu F,\,450$  VDC capacitors in series (C5 and C6).

#### The EMI Filter

A second order, common-mode filter is used. The lowest frequency of operation occurs at the low input voltages. The estimated lowest frequency of operation is 75 kHz. This is important to attenuate the switching noise sufficiently to pass EMI testing.

A good starting point is to assume that 24 dB of attenuation at 75 kHz is needed. That makes the corner frequency of the common-mode filter as:

$$f_C = f_{SW} \cdot 10 \left( \frac{Att}{40} \right)$$

(eq. 35)

where Att is the attenuation needed at the switching frequency in negative dB.

$$f_C = (75 \text{ kHz}) \ 10 \left(\frac{-24}{40}\right) = 18.8 \text{ kHz} \quad (eq. 36)$$

A damping factor of 0.707 or greater is good and it provides a -3.0 dB attenuation at the corner frequency and does not produce ringing in the filter reactances. Assume that the input line impedance is 50 ohms since the regulatory agencies use a LISN (Line Impedance Stabilization Network) which makes the line impedance equal this value. Calculating the values needed in the common-mode inductor (L1) and "X" capacitors (C1 and C4):

$$\begin{split} L &= \frac{R_L \cdot \zeta}{\pi \cdot f_C} = \frac{(50)(0.707)}{\pi \, (18.8 \text{ kHz})} = 598 \, \mu\text{H} \\ C &= \frac{1}{(2\pi f_C)^2 L} = \frac{1}{[2\pi \, (18.8 \text{ kHz})]^2 (598 \, \mu\text{H})} \, ^{(\text{eq. 37})} \\ &= 0.1 \, \mu\text{F} \end{split}$$

Coilcraft offers off-the-shelf common-mode filter chokes (transformers) and the part number closest to this value is E3493. With this filter design a minimum of -40 dB between the frequencies of 500 kHz and 10 MHz can be expected. If later during the EMI testing stage, additional filtering is needed, a third order to the filter design will be added by using a differential-mode filter.

#### **Post Design Modifications**

It was found that the control circuitry drew more quiescent current than anticipated. That made the start-up voltage higher than desired. It was also found that the optoisolator's dark collector leakage current and the timing capacitor's leakage current were responsible for this behavior. D10 and C17 which isolated these elements behind a low reverse leakage diode during the start-up process were added.

#### Performance of the Sample Design

Output Regulation:

Input Regulation:

Output Ripple:

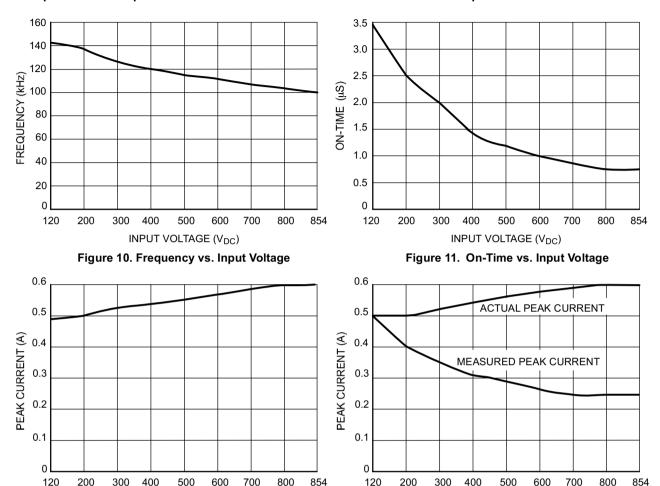

Figures 10 through 13 graphically represent some of the parameters of the evaluation board that are important to its operation. These parameters were measured at full-rated load for all of the outputs.

INPUT VOLTAGE (V<sub>DC</sub>)

Figure 12. Actual Peak Current vs

Input Voltage

Figure 13. Actual and Measured Peak Current vs. Input Voltage

INPUT VOLTAGE (V<sub>DC</sub>)

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

#### **PUBLICATION ORDERING INFORMATION**

Literature Fulfillment:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

**Phone**: 303-675-2175 or 800-344-3860 Toll Free USA/Canada **Fax**: 303-675-2176 or 800-344-3867 Toll Free USA/Canada

Email: ONlit@hibbertco.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

JAPAN: ON Semiconductor, Japan Customer Focus Center 2-9-1 Kamimeguro, Meguro-ku, Tokyo, Japan 153-0051

Phone: 81-3-5773-3850 Email: r14525@onsemi.com

ON Semiconductor Website: http://onsemi.com For additional information, please contact your local Sales Representative. This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.