rfmd.com

## **RF2163**

#### **3V, 2.5 GHz LINEAR POWER AMPLIFIER**

RoHS Compliant & Pb-Free Product Package Style: QFN, 16-Pin, 4 x 4

#### **Features**

- Single 3.3V Power Supply

- +30dBm Saturated Output Power

- 19dB Small Signal Gain

- High Power Added Efficiency

- Patent Pending Power Sense Technology

- 1800 MHz to 2500 MHz Frequency Range

#### **Applications**

- 2.5 GHz ISM Band Applications

- PCS Communication Systems

- Wireless LAN Systems

- Commercial and Consumer Systems

- Portable Battery Powered Equipment

- Broadband Spread-Spectrum Systems

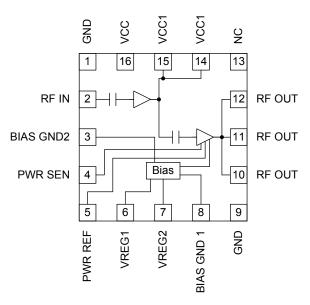

Functional Block Diagram

### **Product Description**

The RF2163 is a linear, medium power, high efficiency amplifier IC designed specifically for low voltage operation. The device is manufactured on an advanced Gallium Arsenide Heterojunction Bipolar Transistor (HBT) process, and has been designed for use as the final RF amplifier in 2.5 GHz spread-spectrum transmitters. The device is provided in a 16-pin leadless chip carrier with a backside ground and is self-contained with the exception of the output matching network and power supply feed line.

#### **Ordering Information**

RF2163 3V, 2.5 GHz Linear Power Amplifier

RF2163PCK-410 Fully assembled evaluation board tuned for 2.4 to 2.5GHz

and 5 piece loose samples

### **Optimum Technology Matching® Applied**

| · p · · · · · · · · · · · · · · · · · · |               |              |            |  |  |

|-----------------------------------------|---------------|--------------|------------|--|--|

| ☑ GaAs HBT                              | ☐ SiGe BiCMOS | ☐ GaAs pHEMT | ☐ GaN HEMT |  |  |

| ☐ GaAs MESFET                           | ☐ Si BiCMOS   | ☐ Si CMOS    |            |  |  |

| ☐ InGaP HBT                             | ☐ SiGe HBT    | ☐ Si BJT     |            |  |  |

RF MICRO DEVICES®, RFMD®, Optimum Technology, Matching®, Enabling Wireless Connectivity<sup>IM</sup>, PowerStar®, POLARIS™ TOTAL RADIO™ and UltimateBlue® are trademarks or RFMD, LLC. BUETOOTH is a trade mark owned by Bulletonth SIG. (by I.I.S. A and Hickesed for use by ERFM). All other trade names is referred as a format overall by Bulletonth SIG. (by I.I.S. A) and Hickesed for use by ERFM. All other trade names are trademarks and the promoter of their researchies warners. (2010) EFF Mirro, Devices for the promoter of their researchies warners. (2010) EFF Mirro, Devices for the promoter of their researchies warners. (2010) EFF Mirro, Devices for the promoter of their researchies warners. (2010) EFF Mirro, Devices for the promoter of their researchies warners.

#### **Absolute Maximum Ratings**

| Parameter                                 | Rating        | Unit     |

|-------------------------------------------|---------------|----------|

| Supply Voltage                            | -0.5 to +6.0  | $V_{DC}$ |

| Power Control Voltage (V <sub>REG</sub> ) | -0.5 to 3.3   | V        |

| DC Supply Current                         | 1000          | mA       |

| Input RF Power                            | +15           | dBm      |

| Operating Ambient Temperature             | -40 to +85    | °C       |

| Storage Temperature                       | -40 to +150   | °C       |

| Moisture sensitivity                      | JEDEC Level 3 |          |

#### Caution! ESD sensitive device.

Exceeding any one or a combination of the Absolute Maximum Rating conditions may cause permanent damage to the device. Extended application of Absolute Maximum Rating conditions to the device may reduce device reliability. Specified typical performance or functional operation of the device under Absolute Maximum Rating conditions is not implied.

RoHS status based on EUDirective 2002/95/EC (at time of this document revision).

The information in this publication is believed to be accurate and reliable. However, no responsibility is assumed by RF Micro Devices, Inc. ("RFMD") for its use, nor for any infringement of patents, or other rights of third parties, resulting from its use. No license is granted by implication or otherwise under any patent or patent rights of RFMD. RFMD reserves the right to change component circuitry, recommended application circuitry and specifications at any time without prior notice.

| Bayanastay                     | Specification |              | 11:4 | O a sadiki a sa |                                                                                              |  |

|--------------------------------|---------------|--------------|------|-----------------|----------------------------------------------------------------------------------------------|--|

| Parameter                      | Min.          | Min. Typ. N  |      | Unit            | Condition                                                                                    |  |

| Overall                        |               |              |      |                 | T=25 °C, V <sub>CC</sub> =3.5V, V <sub>REG1</sub> =V <sub>REG2</sub> =2.3V,<br>Freq=2450 MHz |  |

| Frequency Range                |               | 1800 to 2500 |      | MHz             |                                                                                              |  |

| Maximum Saturated Output Power | +29           | +30          | +32  | dBm             | P <sub>IN</sub> =+13dBm                                                                      |  |

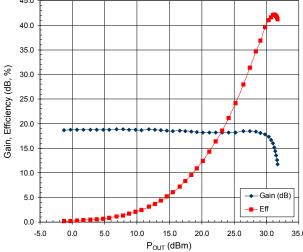

| Efficiency at Max Output Power |               | 26           |      | %               |                                                                                              |  |

| Maximum Linear Output Power    |               | 25           |      | dBm             | With 802.11 modulation (11Mbit/s) and meeting 802.11 spectral mask.                          |  |

| Linear Efficiency              |               | 25           |      | %               |                                                                                              |  |

| Small Signal Gain              | 16            | 19           |      | dB              | P <sub>IN</sub> =10dBm                                                                       |  |

| Reverse Isolation              |               | 30           |      | dB              | In "ON" state                                                                                |  |

|                                |               | 30           |      | dB              | In "OFF" state                                                                               |  |

| Second Harmonic                |               | -35          |      | dBc             | Including second harmonic trap, see application circuit                                      |  |

| Adjacent Channel Power         |               | -35          | -32  | dBc             | P <sub>OUT</sub> =24dBm                                                                      |  |

| Alternate Channel Power        |               | -52          | -50  | dBc             | P <sub>OUT</sub> =24dBm                                                                      |  |

| Isolation                      |               | TBD          |      | dBm             | In "OFF" state, P <sub>IN</sub> =TBD                                                         |  |

| Input Impedance                |               | 50           |      | Ω               | With external matching                                                                       |  |

| Input VSWR                     |               | 2:1          |      |                 | With external matching                                                                       |  |

| Power Down                     |               |              |      |                 |                                                                                              |  |

| V <sub>REG</sub> "ON"          |               | 2.3          |      | V               | Voltage supplied to control input; device is "ON"                                            |  |

| V <sub>REG</sub> "OFF"         |               | 0            | 0.5  | V               | Voltage supplied to control input; device is "OFF"                                           |  |

| Power Supply                   |               |              |      |                 |                                                                                              |  |

| Operating Voltage              |               | 3.0 to 5.0   |      | V               |                                                                                              |  |

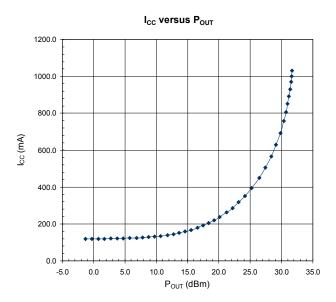

| Current Consumption            |               | 650          |      | mA              | Power Down "ON", at max output power                                                         |  |

|                                |               | 350          |      | mA              | Power Down "ON", P <sub>OUT</sub> =25dBm                                                     |  |

|                                |               | 150          | 290  | mA              | Idle current                                                                                 |  |

rfmd.com

| Pin  | Function  | Description                                                                                                                                       | Interface Schematic    |  |

|------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|

| 1    | GND       | Ground connection. For best performance, keep traces physically short                                                                             |                        |  |

|      |           | and connect immediately to ground plane.                                                                                                          |                        |  |

| 2    | RF IN     | RF input. This input is AC coupled, so an external blocking capacitor is not required if this pin is connected to a DC path.                      | VCC1                   |  |

|      |           |                                                                                                                                                   | Dand Min               |  |

|      |           |                                                                                                                                                   | Bond Wire Inductance   |  |

|      |           |                                                                                                                                                   | RF IN O                |  |

|      |           |                                                                                                                                                   | BIAS                   |  |

| 3    | BIAS GND2 | Ground for second stage bias circuit. For best performance, keep traces physically short and connect immediately to ground plane.                 | See pin 16.            |  |

| 4    | PWR SEN   | The PWR SEN and PWR REF pins can be used in conjunction with an external feedback path to provide an RF power control function for the RF2163.    | RF OUT                 |  |

|      |           | The power control function is based on sampling the RF drive to the final                                                                         |                        |  |

|      |           | stage of the RF2163.                                                                                                                              | PWR SEN                |  |

|      |           |                                                                                                                                                   | \\                     |  |

|      |           |                                                                                                                                                   |                        |  |

|      |           |                                                                                                                                                   | PWR REF                |  |

|      |           |                                                                                                                                                   | BIAS                   |  |

|      |           |                                                                                                                                                   | =                      |  |

| 5    | PWR REF   | Same as pin 4.                                                                                                                                    | See pin 4.             |  |

| 6    | VREG1     | This pin requires a regulated supply to maintain the correct bias current.                                                                        | See pin 16.            |  |

| 7    | VREG2     | Same as pin 6.                                                                                                                                    | See pin 16.            |  |

| 8    | BIAS GND1 | Ground for first stage bias circuit. For best performance connect to ground with a 10nH inductor.                                                 | See pin 16.            |  |

| 9    | GND       | Same as pin 1.                                                                                                                                    |                        |  |

| 10   | RF OUT    | RF output and bias for the output stage. The power supply for the output transistor needs to be supplied to this pin. This can be done through a  | RF OUT                 |  |

|      |           | quarter-wave length microstrip line that is RF grounded at the other end, or through an RF inductor that supports the required DC currents.       | BIAS                   |  |

|      |           | though an Ki muuctoi that supports the required DC currents.                                                                                      | =                      |  |

| 11   | RF OUT    | Same as pin 10.                                                                                                                                   | See pin 10.            |  |

| 12   | RF OUT    | Same as pin 10.                                                                                                                                   | See pin 10.            |  |

| 13   | NC        | Not connected.                                                                                                                                    |                        |  |

| 14   | VCC1      | Interstage match and bias for first stage output. Connect interstage matching capacitor to t pin with a short trace. Connect low-frequency bypass | See pin 2.             |  |

|      |           | capacitors to this pin with a long trace. See evaluation board layout for                                                                         |                        |  |

| 15   | VCC1      | details. Same as pin 14.                                                                                                                          | See pin 2.             |  |

| 16   | VCC       | Power supply pin for the bias circuits. External low frequency bypass capac-                                                                      | VCC                    |  |

| _•   |           | itors should be connected if no other low frequency decoupling is nearby.                                                                         | VCC                    |  |

|      |           |                                                                                                                                                   | VREG1 O-               |  |

|      |           |                                                                                                                                                   | VREG2 O-               |  |

|      |           |                                                                                                                                                   |                        |  |

|      |           |                                                                                                                                                   | BIAS BIAS<br>GND1 GND2 |  |

| Pkg  | GND       | Ground connection. The backside of the package should be connected to                                                                             | See pin 1 and 2.       |  |

| Base |           | the ground plane through a short path, i.e., vias under the device may be required.                                                               |                        |  |

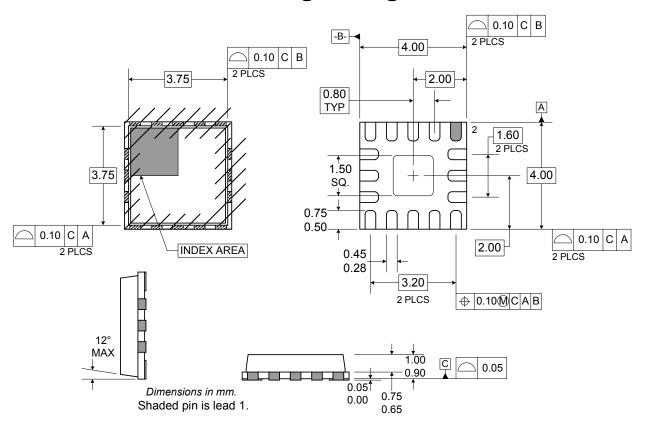

## **Package Drawing**

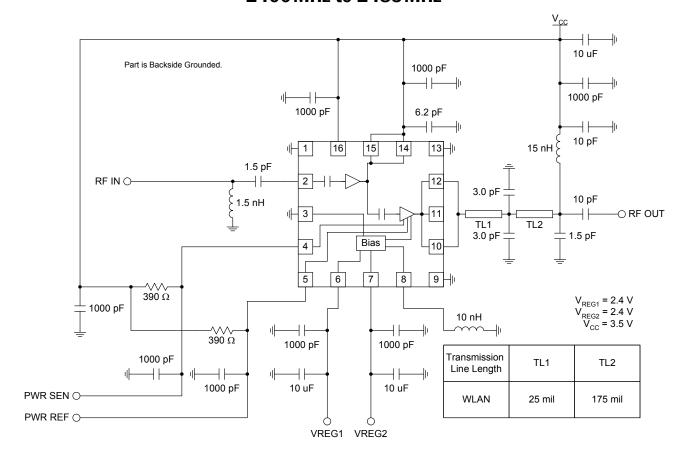

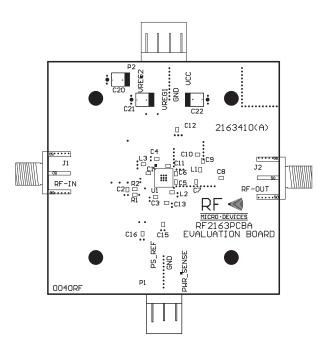

# Application Schematic 2400 MHz to 2483 MHz

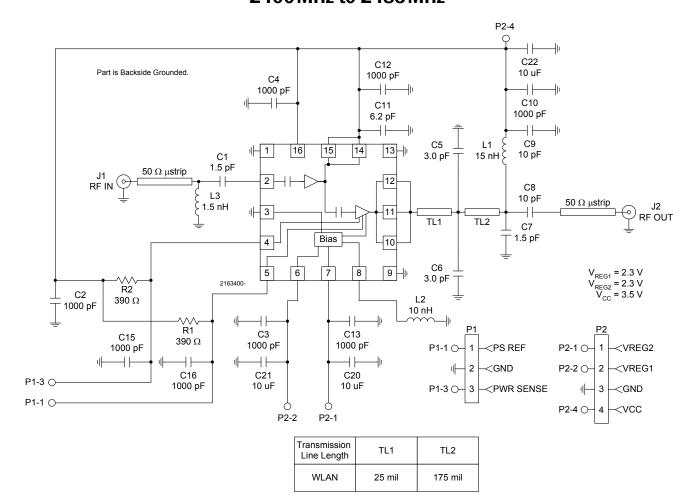

# Evaluation Board Schematic 2400 MHz to 2483 MHz

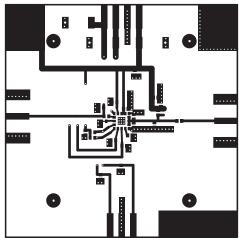

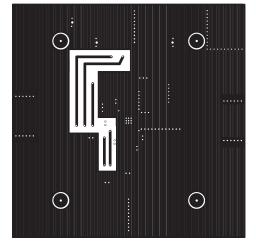

# Evaluation Board Layout Board Size 2.0" x 2.0"

Board Thickness 0.028", Board Material FR-4

## **RF2163**

### **Theory of Operation and Application Information**

The RF2163 is a two-stage device with a nominal gain of 19dB in the 2.4GHz to 2.5GHz ISM band. The RF2163 is designed primarily for IEEE802.11B WLAN applications where the available supply voltage and current are not limited. It will meet 802.11B spectral mask requirements at an output power of +24dBm. It is especially appropriate for WLAN access points and other base-station type equipment.

The RF2163 requires only a single positive supply of 3.3V nominal (or greater) to operate to full specifications. Power control is provided through two bias control input pins ( $V_{REG1}$  and  $V_{REG2}$ ), but in most applications these are tied together and used as a single control input.

There is some external matching on the input and output of the part, thus allowing the part to be used in other applications outside the 2.4 GHz to 2.5 GHz ISM band (such as MMDS). Both the input and the output of the device need a series DC-blocking capacitor. In some cases, a capacitor used as a matching component can also serve as the blocking cap. The circuit used on the evaluation board is optimized for 3.5 V nominal applications.

For best results, the PA circuit layout from the evaluation board should be copied as closely as possible, particularly the ground layout and ground vias. Other configurations may also work, but the design process is much easier and quicker if the layout is copied from the RF2163 evaluation board. Gerber files of our designs can be provided upon request.

The RF2163 is not a difficult part to implement, but care in circuit layout and component selection is always advisable when designing circuits to operate at 2.5 GHz. The most critical passive components in the circuit are the input, interstage and output matching components (C1, C5, C6, C7, and C11). In these cases, high-Q capacitors suitable for RF applications are used on our evaluation board (a BOM is available on request). High-Q parts are not required in every design, but it is very strongly recommended that the original design be implemented with the same or similar parts used on our evaluation board. Then, less costly components can be substituted in their place, making it easy to test the impact of cheaper components on performance. General RFMD experience has indicated that the slightly higher cost of better quality passive components is more than offset by the significant improvements in production yields in large-volume manufacturing.

The interstage matching capacitor, C11, along with the combined inductance of the internal bond wire, the short length of circuit board trace, and the parasitic inductance of this capacitor, tunes the peak of the small-signal gain response. The trace length between C11 and pins 14 and 15 should be kept as short as possible.

In practice,  $V_{CC1}$ ,  $V_{CC}$ , and the supply for the output stage bias will be tied to this supply line. This can be accomplished using a suitably-long transmission line which is RF shorted on the other end. Ideally the length of this line will be a quarter wavelength, but it only needs to be long enough so that the effects of other supply bypass capacitors on the interstage match are minimized. If board space is a concern, this isolation can also be accomplished with an RF choke inductor or ferrite bead. Additionally, a higher-value capacitor than shown on the application schematic can be used if bypass capacitors must be closer. A Smith Chart can be used to provide initial guidance for value selection and parts placement. Be aware of the self-resonant frequency (SRF) of higher-valued capacitors. The SRF must be above the frequency of operation.

The output matching caps are C5, C6, and C7. These are tuned along with the  $50\Omega$  transmission line segments TL1 and TL2, as shown on the evaluation board schematic. These segments should be duplicated as closely as possible. Due to variations in FR-4 characteristics and PCB manufacturer process variations, some benefit will be obtained from small adjustments to these transmission line lengths when the evaluation board layout is duplicated on another design. Prior to full rate manufacturing, the board layout of early prototypes should include some additional exposed ground areas around C5, C6, and C7 to optimize this part of the circuit. In order to reduce component count, the output can also be tuned with a single capacitor. A Smith Chart can help determine the desired value and transmission line length, which can be similarly adjusted on the board prior to production. This will result in a slightly lower-bandwidth and more sensitive match, but in most applications the bandwidth is still sufficient.

rfmd.com

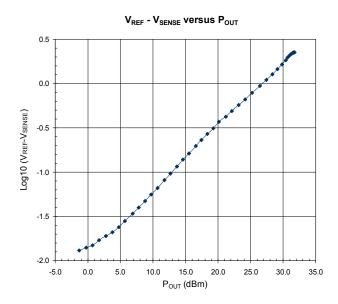

Power sensing is implemented with the PWR SEN and PWR REF lines. The outputs of these pins are transistor collectors and need to be pulled up to the supply through a resistor. PWR REF provides an output current proportional to the output stage bias current, and PWR SEN provides an output current proportional to the total (RF and bias) current of the output stage. The pull-lup resistors convert these currents to voltages, and the voltage difference between these two pins is proportional to the RF current. See the graph, " $V_{REF}$ - $V_{SENSE}$  versus  $P_{OUT}$ ", for the response of this signal. This difference signal can be fed to a power control circuit elsewhere in the end product, or it can be processed at the PA with additional circuitry and used to adjust the  $V_{REG}$  voltage(s) to implement automatic level control. Contact RFMD Sales or Applications Engineering for additional data and guidance in using this feature.

The RF2163 has primarily been characterized with a voltage on  $V_{REG1}$  and  $V_{REG2}$  of 2.4VDC. However, the RF2163 will operate from a wide range of control voltages. If you prefer to use a control voltage that is significantly different than 2.4VDC, contact RFMD Sales or Applications Engineering for additional data and guidance.

## **RF2163**