# SIEMENS

## Standard EEPROM ICs

SLx 24C04

4 Kbit (512  $\times$  8 bit) Serial CMOS-EEPROM with I<sup>2</sup>C Synchronous 2-Wire Bus

Data Sheet 1998-07-27

| SLx 24C04<br>Revision His        | story:                          | Current Version: 1998-07-27                                             |

|----------------------------------|---------------------------------|-------------------------------------------------------------------------|

| Previous Version:                |                                 | 06.97                                                                   |

| Page<br>(in previous<br>Version) | Page<br>(in current<br>Version) | Subjects (major changes since last revision)                            |

| 3                                | 3                               | Text was changed to "Typical programming time 5 ms for up to 16 bytes". |

| 4, 5                             | 4, 4                            | CS0, CS1 and CS2 were replaced by n.c.                                  |

| 5                                | _                               | The paragraph "Chip Select (CS0, CS1, CS2)" was removed completely.     |

| 5                                | 5                               | WP = $V_{\rm CC}$ protects the upper half entire memory.                |

| 11, 12                           | 11, 12                          | The erase/write cycle is finished latest after <del>10</del> 8 ms.      |

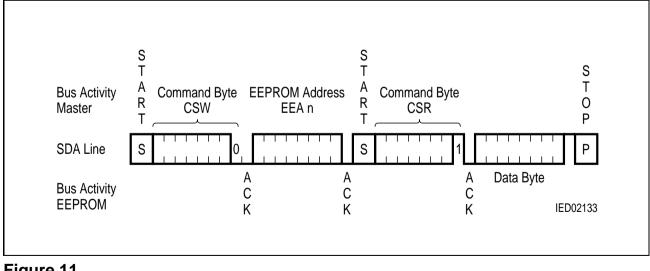

| 15                               | 15                              | Figure 11: second command byte is a <b>CSR</b> and not CSW.             |

| 19                               | 19                              | "Capacitive load" were added.                                           |

| 20                               | 20                              | Some timings were changed.                                              |

| 20                               | 20                              | The line "erase/write cycle" was removed.                               |

| 20                               | 20                              | Chapter 7.4 "Erase and Write Characteristics" has been added.           |

#### I<sup>2</sup>C Bus

Purchase of Siemens I<sup>2</sup>C components conveys the license under the Philips I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C system provided the system conforms to the I<sup>2</sup>C specifications defined by Philips.

#### Edition 1998-07-27

Published by Siemens AG, Bereich Halbleiter, Marketing-Kommunikation, Balanstraße 73, 81541 München

© Siemens AG 1998. All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or the Siemens Companies and Representatives worldwide (see address list).

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

#### Packing

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

#### Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Semiconductor Group of Siemens AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Semiconductor Group of Siemens AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

# SIEMENS

# 4 Kbit (512 $\times$ 8 bit) Serial CMOS EEPROMs, I<sup>2</sup>C Synchronous 2-Wire Bus

SLx 24C04

#### Features

- Data EEPROM internally organized as 512 bytes and 32 pages × 16 bytes

- Low power CMOS

- V<sub>cc</sub> = 2.7 to 5.5 V operation

- Two wire serial interface bus, I<sup>2</sup>C-Bus compatible

- Filtered inputs for noise suppression with Schmitt trigger

- Clock frequency up to 400 kHz

- High programming flexibility

- Internal programming voltage

- Self timed programming cycle including erase

- Byte-write and page-write programming, between 1 and 16 bytes

- Typical programming time 5 ms for up to 16 bytes

- High reliability

- Endurance 10<sup>6</sup> cycles<sup>1)</sup>

- Data retention 40 years<sup>1)</sup>

- ESD protection 4000 V on all pins

- 8 pin DIP/DSO packages

- Available for extended temperature ranges

- Industrial: 40 °C to + 85 °C

- Automotive:  $-40 \degree C$  to + 125  $\degree C$

Semiconductor Group

<sup>&</sup>lt;sup>1)</sup> Values are temperature dependent, for further information please refer to your Siemens Sales office.

### **Ordering Information**

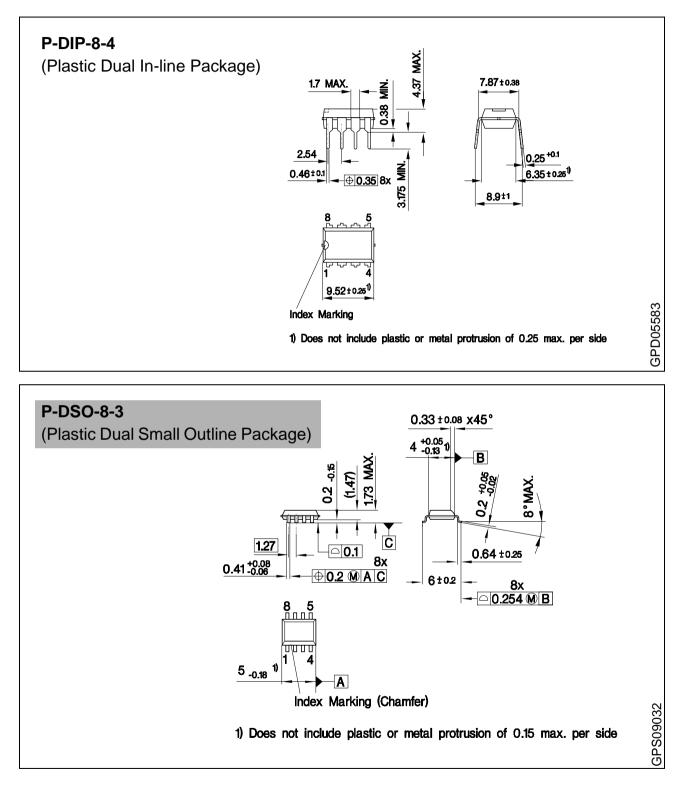

| Туре          | Ordering Code | Package   | Temperature     | Voltage    |

|---------------|---------------|-----------|-----------------|------------|

| SLA 24C04-D   | Q67100-H3549  | P-DIP-8-4 | – 40 °C + 85 °C | 4.5 V5.5 V |

| SLA 24C04-S   | Q67100-H3529  | P-DSO-8-3 | – 40 °C + 85 °C | 4.5 V5.5 V |

| SLA 24C04-D-3 | Q67100-H3434  | P-DIP-8-4 | – 40 °C + 85 °C | 2.7 V5.5 V |

| SLA 24C04-S-3 | Q67100-H3528  | P-DSO-8-3 | – 40 °C + 85 °C | 2.7 V5.5 V |

| SLE 24C04-D   | Q67100-H3223  | P-DIP-8-4 | – 40°C + 125 °C | 4.5 V5.5 V |

| SLE 24C04-S   | Q67100-H3224  | P-DSO-8-3 | – 40°C + 125 °C | 4.5 V5.5 V |

Other types are available on request

- Temperature range (- 55 °C ... + 150 °C)

- Package (die, wafer delivery)

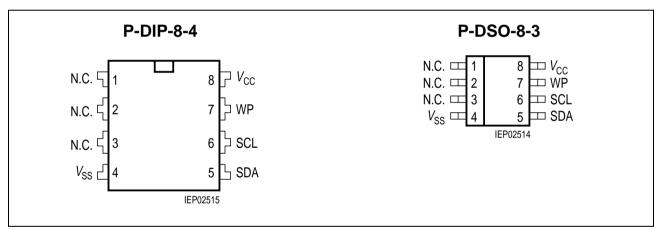

### 1 Pin Configuration

#### Figure 1 Pin Configuration (top view)

## **Pin Definitions and Functions**

#### Table 1

| Pin No. | Symbol          | Function                      |

|---------|-----------------|-------------------------------|

| 1, 2, 3 | N. C.           | Not connected                 |

| 4       | V <sub>SS</sub> | Ground                        |

| 5       | SDA             | Serial bidirectional data bus |

| 6       | SCL             | Serial clock input            |

| 7       | WP              | Write protection input        |

| 8       | V <sub>cc</sub> | Supply voltage                |

### **Pin Description**

#### Serial Clock (SCL)

The SCL input is used to clock data into the device on the rising edge and to clock data out of the device on the falling edge.

#### Serial Data (SDA)

SDA is a bidirectional pin used to transfer addresses, data or control information into the device or to transfer data out of the device. The output is open drain, performing a wired AND function with any number of other open drain or open collector devices. The SDA bus requires a pull-up resistor to  $V_{\rm CC}$ .

#### Write Protection (WP)

WP switched to  $V_{\rm SS}$  allows normal read/write operations.

WP switched to  $V_{\rm CC}$  protects the entire EEPROM against changes (hardware write protection).

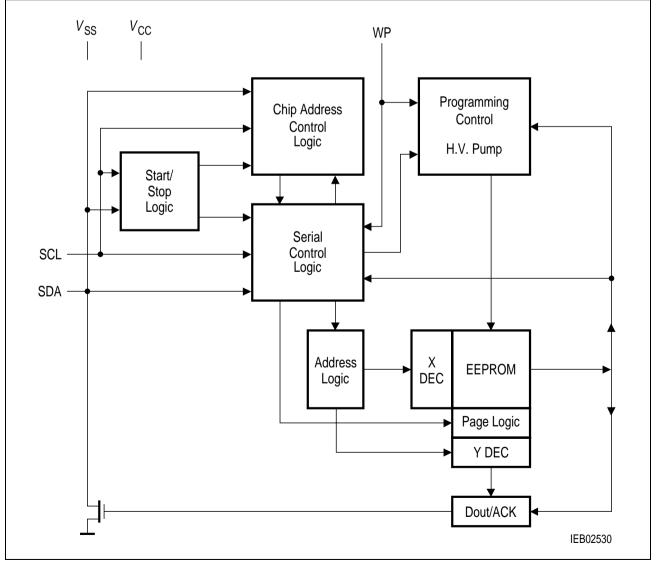

### 2 Description

The SLx 24C04 device is a serial electrically erasable and programmable read only memory (EEPROM), organized as  $512 \times 8$  bit. The data memory is divided into 32 pages. The 16 bytes of a page can be programmed simultaneously.

The device conforms to the specification of the 2-wire serial  $I^2C$ -Bus. Low voltage design permits operation down to 2.7 V with low active and standby currents.

The device operates at 5.0 V ± 10% with a maximum clock frequency of 400 kHz and at 2.7 ... 4.5 V with a maximum clock frequency of 100 kHz. The device is available as 5 V type ( $V_{\rm CC}$  = 4.5 ... 5.5 V) with two temperature ranges for industrial and automotive applications and as 3 V type ( $V_{\rm CC}$  = 2.7 ... 5.5 V) for industrial applications. The EEPROMs are mounted in eight-pin DIP and DSO packages or are also supplied as chips.

#### Figure 2 Block Diagram

Semiconductor Group

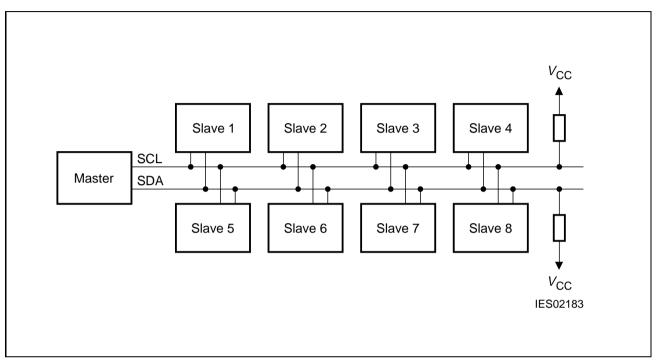

#### 3 I<sup>2</sup>C-Bus Characteristics

The SLx 24C04 devices support a master/slave bidirectional bus oriented protocol in which the EEPROM always takes the role of a slave.

#### Figure 3 Bus Configuration

**Master** Device that initiates the transfer of data and provides the clock for both transmit and receive operations.

**Slave** Device addressed by the master, capable of receiving and transmitting data.

- **Transmitter** The device with the SDA as output is defined as the transmitter. Due to the open drain characteristic of the SDA output the device applying a low level wins.

- **Receiver** The device with the SDA as input is defined as the receiver.

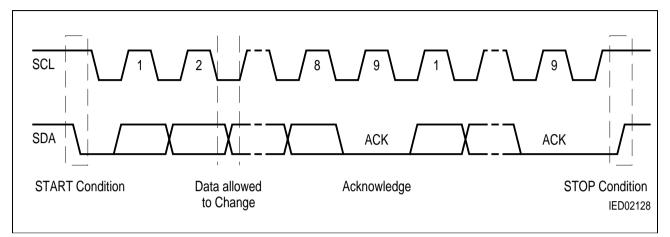

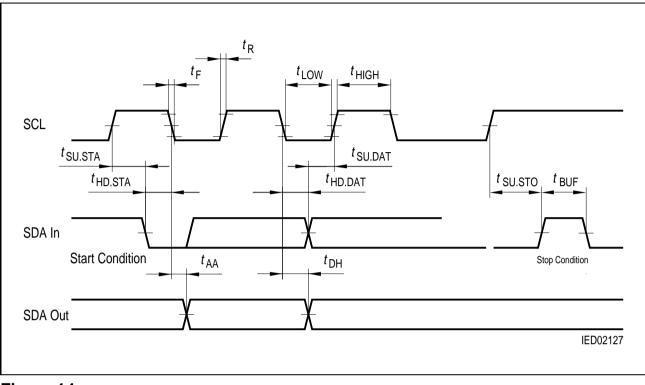

The conventions for the serial clock line and the bidirectional data line are shown in **figure 4**.

#### Figure 4

${\bf I}^2 \mbox{C-Bus}$  Timing Conventions for START Condition, STOP Condition, Data Validation and Transfer of Acknowledge ACK

| Standby         | Mode in which the bus is not busy (no serial transmission, no programming): both clock (SCL) and data line (SDA) are in high state. The device enters the standby mode after a STOP condition or after a programming cycle.                                                                                                                                                                                                                                                                                                                 |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START Condition | High to low transition of SDA when SCL is high, preceding all commands.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| STOP Condition  | Low to high transition of SDA when SCL is high, terminating all communications. A STOP condition initiates an EEPROM programming cycle. A STOP condition after reading a data byte from the EEPROM initiates the Standby mode.                                                                                                                                                                                                                                                                                                              |

| Acknowledge     | A successful reception of eight data bits is indicated by the receiver by pulling down the SDA line during the following clock cycle of SCL (ACK). The transmitter on the other hand has to release the SDA line after the transmission of eight data bits. The EEPROM as the receiving device responds with an acknowledge, when addressed. The master, on the other side, acknowledges each data byte transmitted by the EEPROM and can at any time end a read operation by releasing the SDA line (no ACK) followed by a STOP condition. |

| Data Transfer   | Data must change only during low SCL state, data remains valid<br>on the SDA bus during high SCL state. Nine clock pulses are<br>required to transfer one data byte, the most significant bit (MSB)<br>is transmitted first.                                                                                                                                                                                                                                                                                                                |

#### 4 Device Addressing and EEPROM Addressing

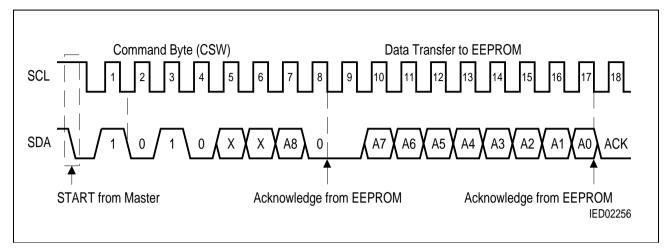

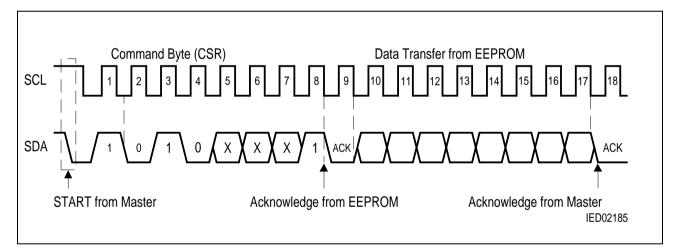

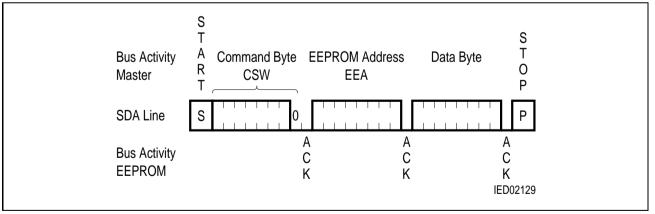

After a START condition, the master always transmits a Command Byte CSW or CSR. After the acknowledge of the EEPROM a Control Byte follows, its content and the transmitter depend on the previous Command Byte. The description of the Command and Control Bytes is shown in **table 2**.

**Command Byte** Selects operation: the least significant bit b0 is low for a write operation (<u>Chip Select Write Command Byte CSW</u>) or set high for a read operation (<u>Chip Select Read Command Byte CSR</u>).

**Contains address information:** in the CSW Command Byte, the bit position b1 is decoded for the uppermost EEPROM address bit A8 (in the CSR Command Byte, the bit positions b3 to b1 are left undefined, in the CSW Command Byte, the bit positions b3 and b2 as well).

**Control Byte** Following CSW (b0 = 0): contains the eight lower bits of the EEPROM address (EEA) bit A7 to A0.

**Following CSR (b0 = 1):** contains the data read out, transmitted by the EEPROM. The EEPROM data are read as long as the master pulls down SDA after each byte in order to acknowledge the transfer. The read operation is stopped by the master by releasing SDA (no acknowledge is applied) followed by a STOP condition.

## Table 2Command and Control Byte for I<sup>2</sup>C-Bus Addressing of Chip and EEPROM

|     | Definition |    |    |    |    |    | Function |    |                       |

|-----|------------|----|----|----|----|----|----------|----|-----------------------|

|     | b7         | b6 | b5 | b4 | b3 | b2 | b1       | b0 |                       |

| CSW | 1          | 0  | 1  | 0  | х  | х  | A8       | 0  | Chip Select for Write |

| CSR | 1          | 0  | 1  | 0  | х  | х  | х        | 1  | Chip Select for Read  |

| EEA | A7         | A6 | A5 | A4 | A3 | A2 | A1       | A0 | EEPROM address        |

The device has an internal address counter which points to the current EEPROM address.

The address counter is incremented

- after a data byte to be written has been acknowledged, during entry of further data byte

- during a byte read, thus the address counter points to the following address after reading a data byte.

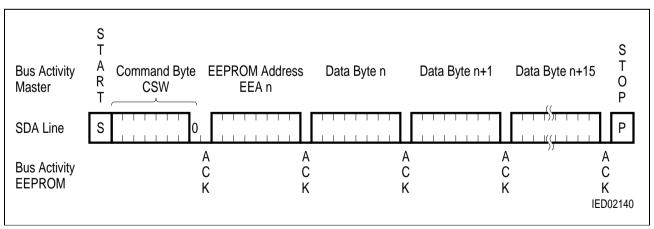

#### The timing conventions for read and write operations are described in figures 5 and 6.

### Figure 5 Timing of the Command Byte CSW

#### 5 Write Operations

Changing of the EEPROM data is initiated by the master with the command byte CSW. Depending on the state of the Write Protection pin WP either one byte (Byte Write) or up to 16 bytes (Page Write) are modified in one programming procedure.

#### 5.1 Byte Write

- Address Setting After a START condition the master transmits the Chip Select Write byte CSW. The EEPROM acknowledges the CSW byte during the ninth clock cycle. The following byte with the EEPROM address (A0 to A7) is loaded into the address counter of the EEPROM and acknowledged by the EEPROM.

- **Transmission of Data** Finally the master transmits the data byte which is also acknowledged by the EEPROM into the internal buffer.

- **Programming Cycle** Then the master applies a STOP condition which starts the internal programming procedure. The data bytes are written in the memory location addressed in the EEA byte (A0 to A7) and the CSW byte (A8). The programming procedure consists of an internally timed erase/write cycle. In the first step, the selected byte is erased to "1". With the next internal step, the addressed byte is written according to the contents of the buffer.

#### Figure 7 Byte Write Sequence

The erase/write cycle is finished latest after 8 ms. Acknowledge polling may be used for speed enhancement in order to indicate the end of the erase/write cycle (refer to **chapter 5.3** Acknowledge Polling).

#### 5.2 Page Write

Address Setting The page write procedure is the same as the byte write procedure up to the first data byte. In a page write instruction however, entry of the EEPROM address byte EEA is followed by a sequence of one to maximum sixteen data bytes with the new data to be programmed. These bytes are transferred to the internal page buffer of the EEPROM.

- **Transmission of Data** The first entered data byte will be stored according to the EEPROM address n given by EEA (A0 to A7) and CSW (A8). The internal address counter is incremented automatically after the entered data byte has been acknowledged. The next data byte is then stored at the next higher EEPROM address. EEPROM addresses within the same page have common page address bits A4 through A8. Only the respective four least significant address bits A0 through A3 are incremented, as all data bytes to be programmed simultaneously have to be within the same page.

- **Programming Cycle** The master stops data entry by applying a STOP condition, which also starts the internally timed erase/write cycle. In the first step, all selected bytes are erased to "1". With the next internal step, the addressed bytes are written according to the contents of the page buffer.

Those bytes of the page that have not been addressed are not included in the programming.

#### Figure 8 Page Write Sequence

The erase/write cycle is finished latest after 8 ms. Acknowledge polling may be used for speed enhancement in order to indicate the end of the erase/write cycle (refer to **chapter 5.3** Acknowledge Polling).

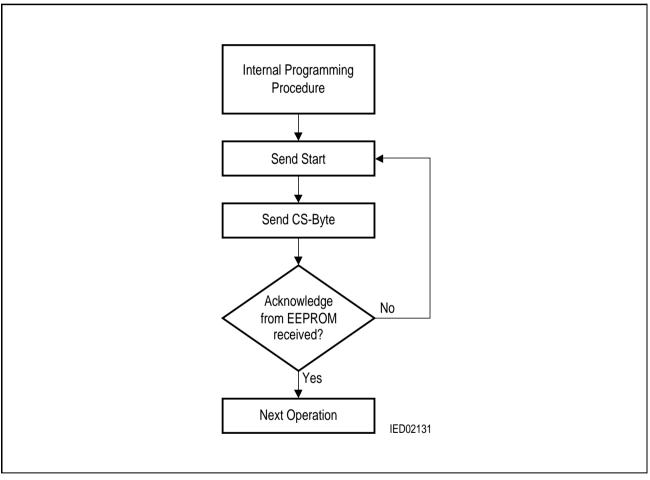

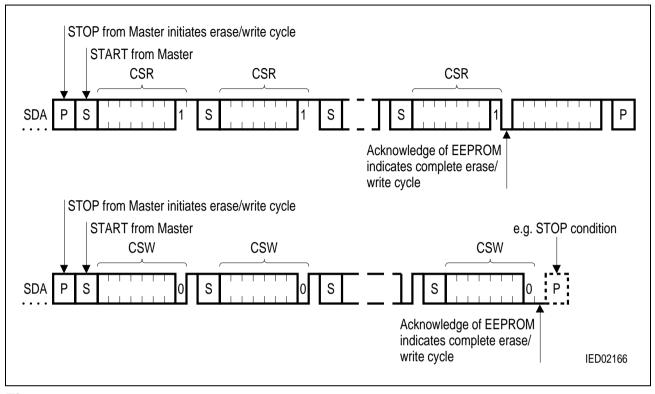

## 5.3 Acknowledge Polling

During the erase/write cycle the EEPROM will not respond to a new command byte until the internal write procedure is completed. At the end of active programming the chip returns to the standby mode and the last entered EEPROM byte remains addressed by the address counter. To determine the end of the internal erase/write cycle acknowledge polling can be initiated by the master by sending a START condition followed by a command byte CSR or CSW (read with b0 = 1 or write with b0 = 0). If the internal erase/ write cycle is not completed, the device will not acknowledge the transmission. If the internal erase/write cycle is completed, the device acknowledges the received command byte and the protocol activities can continue.

#### Figure 9 Flow Chart "Acknowledge Polling"

Figure 10 Principle of Acknowledge Polling

#### 6 Read Operations

Reading of the EEPROM data is initiated by the Master with the command byte CSR.

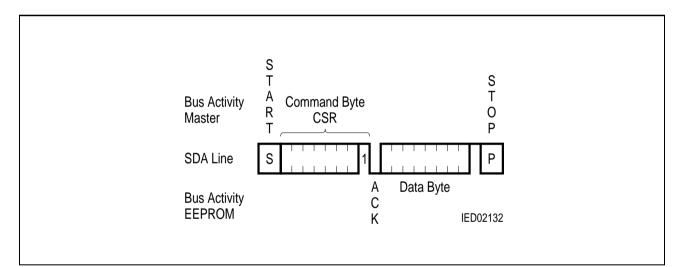

#### 6.1 Random Read

Random read operations allow the master to access any memory location.

- Address Setting The master generates a START condition followed by the command byte CSW. The receipt of the CSW-byte is acknowledged by the EEPROM with a low on the SDA line. Now the master transmits the EEPROM address (EEA) to the EEPROM and the internal address counter is loaded with the desired address.

- **Transmission of CSR** After the acknowledge for the EEPROM address is received, the master generates a START condition, which terminates the initiated write operation. Then the master transmits the command byte CSR for read, which is acknowledged by the EEPROM.

Transmission of<br/>EEPROM DataDuring the next eight clock pulses the EEPROM transmits the<br/>data byte and increments the internal address counter.

STOP Condition fromDuring the following clock cycle the masters releases the busMasterand then transmits the STOP condition.

#### Figure 11 Random Read

#### 6.2 Current Address Read

The EEPROM content is read without setting an EEPROM address, in this case the current content of the address counter will be used (e.g. to continue a previous read operation after the Master has served an interrupt).

| Transmission of CSR            | For a current address read the master generates a START condition, which is followed by the command byte CSR ( <u>chip</u> <u>select read</u> ). The receipt of the CSR-byte is acknowledged by the EEPROM with a low on the SDA line. |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transmission of<br>EEPROM Data | During the next eight clock pulses the EEPROM transmits the data byte and increments the internal address counter.                                                                                                                     |

| STOP Condition from<br>Master  | During the following clock cycle the masters releases the bus and then transmits the STOP condition.                                                                                                                                   |

#### Figure 12 Current Address Read

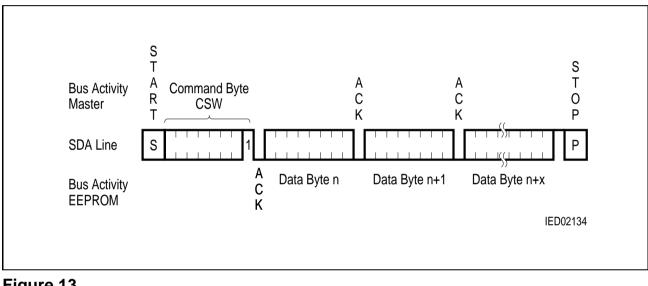

#### 6.3 Sequential Read

A sequential read is initiated in the same way as a current read or a random read except that the master acknowledges the data byte transmitted by the EEPROM. The EEPROM then continues the data transmission. The internal address counter is incremented by one during each data byte transmission.

A sequential read allows the entire memory to be read during one read operation. After the highest addressable memory location is reached, the internal address pointer "rolls over" to the address 0 and the sequential read continues.

The transmission is terminated by the master by releasing the SDA line (no acknowledge) and generating a STOP condition (see **figure 13**).

Figure 13 Sequential Read

## 7 Electrical Characteristics

The listed characteristics are ensured over the operating range of the integrated circuit. Typical characteristics specify mean values expected over the production spread. If not otherwise specified, typical characteristics apply at  $T_A = 25$  °C and the given supply voltage.

### 7.1 Absolute Maximum Ratings

Stresses above those listed here may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of this data sheet is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

| Parameter                     |                                              | Limit Values                  | Units    |

|-------------------------------|----------------------------------------------|-------------------------------|----------|

| Operating temperature         | range 1 (industrial)<br>range 2 (automotive) | - 40 to + 85<br>- 40 to + 125 | °C<br>°C |

| Storage temperature           |                                              | – 65 to + 150                 | °C       |

| Supply voltage                |                                              | - 0.3 to + 7.0                | V        |

| All inputs and outputs with r | $-0.3$ to $V_{\rm CC}$ + 0.5                 | V                             |          |

| ESD protection (human bod     | y model)                                     | 4000                          | V        |

### 7.2 DC Characteristics

| Parameter                               | Symbol          | Lin   | nit Val | ues                   | Units | Test Condition                                    |  |

|-----------------------------------------|-----------------|-------|---------|-----------------------|-------|---------------------------------------------------|--|

|                                         |                 | min.  | typ.    | max.                  |       |                                                   |  |

| Supply voltage                          | V <sub>cc</sub> | 4.5   |         | 5.5                   | V     | 5 V type                                          |  |

|                                         | V <sub>cc</sub> | 2.7   |         | 5.5                   | V     | 3 V type                                          |  |

| Supply current <sup>1)</sup><br>(write) | I <sub>cc</sub> |       | 1       | 3                     | mA    | $V_{\rm CC}$ = 5 V; $f_{\rm c}$ = 100 kHz         |  |

| Standby<br>current <sup>2)</sup>        | I <sub>SB</sub> |       |         | 50                    | μA    | Inputs at $V_{\rm CC}$ or $V_{\rm SS}$            |  |

| Input leakage current                   | I               |       | 0.1     | 10                    | μA    | $V_{\rm IN}$ = $V_{\rm CC}$ or $V_{\rm SS}$       |  |

| Output leakage current                  | I <sub>LO</sub> |       | 0.1     | 10                    | μA    | $V_{\rm OUT} = V_{\rm CC} \text{ or } V_{\rm SS}$ |  |

| Input low<br>voltage                    | $V_{\rm IL}$    | - 0.3 |         | $0.3 	imes V_{ m cc}$ | V     |                                                   |  |

| Parameter                            | Symbol           | Lin                   | nit Val | Units                 | Test Condition |                                                                                      |  |

|--------------------------------------|------------------|-----------------------|---------|-----------------------|----------------|--------------------------------------------------------------------------------------|--|

|                                      |                  | min.                  | typ.    | max.                  |                |                                                                                      |  |

| Input high<br>voltage                | V <sub>IH</sub>  | $0.7 	imes V_{ m cc}$ |         | V <sub>cc</sub> + 0.5 | V              |                                                                                      |  |

| Output low<br>voltage                | V <sub>OL</sub>  |                       |         | 0.4                   | V              | $I_{\rm OL}$ = 3 mA; $V_{\rm CC}$ = 5 V<br>$I_{\rm OL}$ = 2.1 mA; $V_{\rm CC}$ = 3 V |  |

| Input/output<br>capacitance<br>(SDA) | C <sub>I/O</sub> |                       |         | 8 <sup>3)</sup>       | pF             | $V_{\rm IN} = 0 \text{ V}; V_{\rm CC} = 5 \text{ V}$                                 |  |

| Input<br>capacitance<br>(other pins) | C <sub>IN</sub>  |                       |         | 6 <sup>3)</sup>       | pF             | $V_{\rm IN} = 0 \text{ V}; V_{\rm CC} = 5 \text{ V}$                                 |  |

| Capacitive load for each bus line    | C <sub>b</sub>   |                       |         | 400                   | pF             |                                                                                      |  |

## 7.2 DC Characteristics (cont'd)

<sup>1)</sup> The values for  $I_{cc}$  are maximum peak values

<sup>2)</sup> Valid over the whole temperature range

<sup>3)</sup> This parameter is characterized only

#### 7.3 AC Characteristics

| Parameter                                                     | Symbol              |      | Limit Values $V_{\rm cc}$ = 2.7-5.5 V |      | Limit Values $V_{cc}$ = 4.5-5.5 V |     |

|---------------------------------------------------------------|---------------------|------|---------------------------------------|------|-----------------------------------|-----|

|                                                               |                     | min. | max.                                  | min. | max.                              |     |

| SCL clock frequency                                           | $f_{\rm SCL}$       |      | 100                                   |      | 400                               | kHz |

| Clock pulse width low                                         | t <sub>low</sub>    | 4.7  |                                       | 1.2  |                                   | μs  |

| Clock pulse width high                                        | t <sub>high</sub>   | 4.0  |                                       | 0.6  |                                   | μs  |

| SDA and SCL rise time                                         | t <sub>R</sub>      |      | 1000                                  | 1)   | 300                               | ns  |

| SDA and SCL fall time                                         | t <sub>F</sub>      |      | 300                                   | 1)   | 300                               | ns  |

| Start set-up time                                             | t <sub>SU.STA</sub> | 4.7  |                                       | 0.6  |                                   | μs  |

| Start hold time                                               | t <sub>HD.STA</sub> | 4.0  |                                       | 0.6  |                                   | μs  |

| Data in set-up time                                           | t <sub>SU.DAT</sub> | 200  |                                       | 100  |                                   | ns  |

| Data in hold time                                             | t <sub>HD.DAT</sub> | 0    |                                       | 0    |                                   | μs  |

| SCL low to SDA data out valid                                 | t <sub>AA</sub>     | 0.1  | 4.5                                   | 0.1  | 0.9                               | μs  |

| Data out hold time                                            | t <sub>DH</sub>     | 100  |                                       | 50   |                                   | ns  |

| Stop set-up time                                              | t <sub>SU.STO</sub> | 4.0  |                                       | 0.6  |                                   | μs  |

| Time the bus must be free before a new transmission can start | t <sub>BUF</sub>    | 4.7  |                                       | 1.2  |                                   | μs  |

| SDA and SCL spike suppression time at constant inputs         | t <sub>l</sub>      | 50   | 100                                   | 50   | 100                               | ns  |

<sup>1)</sup> The minimum rise and fall times can be calculated as follows: 20 + (0.1/pF) ×  $C_{\rm b}$  [ns] Example:  $C_{\rm b}$  = 100 pF  $\rightarrow t_{\rm R}$  = 20 + 0.1 × 100 [ns] = 30 ns

#### 7.4 Erase and Write Characteristics

| Parameter                      | Symbol          | Limit Values $V_{\rm cc}$ = 2.7-5.5 V |      | Limit $V_{\rm cc} = 4$ | Units |    |

|--------------------------------|-----------------|---------------------------------------|------|------------------------|-------|----|

|                                |                 | typ.                                  | max. | typ.                   | max.  |    |

| Erase + write cycle (per page) | t <sub>WR</sub> | 5                                     | 8    | 5                      | 8     | ms |

| Erase page protection bit      |                 | 2.5                                   | 4    | 2.5                    | 4     | ms |

| Write page protection bit      |                 | 2.5                                   | 4    | 2.5                    | 4     | ms |

Figure 14 Bus Timing Data

#### 8 Package Outlines

#### Sorts of Packing

Package outlines for tubes, trays etc. are contained in our Data Book "Package Information".

SMD = Surface Mounted Device

Dimensions in mm