# **PWM Power Control for DC Loads**

### **Description**

The U2352B bipolar circuit is a PWM device for controlling logic level Power MOSFETs and IGBTs. It allows simple power control for dc loads. Integrated load current monitoring with adjustable switch-off threshold also gives the option of measuring the load current via the MOS transistor's on-state resistance,  $R_{DS(on)}$ , or via a shunt resistor.

#### **Special Features**

- Pulse width control up to 50 kHz clock frequency

- Load current monitoring via the on-state resistance, R<sub>DS(on)</sub>, of the FET or via shunt resistor (optional)

- 100 mA push-pull output stage

- Voltage monitoring

- Temperature-compensated supply voltage limitation

- Chip temperature monitoring

### **Applications**

- Battery-operated screwdrivers

- Battery-operated machine tools

- Halogen lamp controllers

- Dimmers

- Electronic fuses

- High-performance clock generators

Package: DIP8, SO8

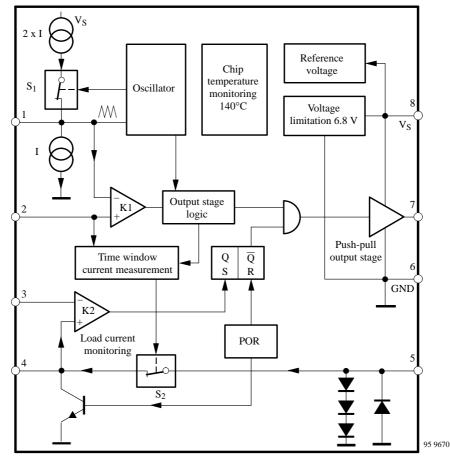

Figure 1. Block diagram

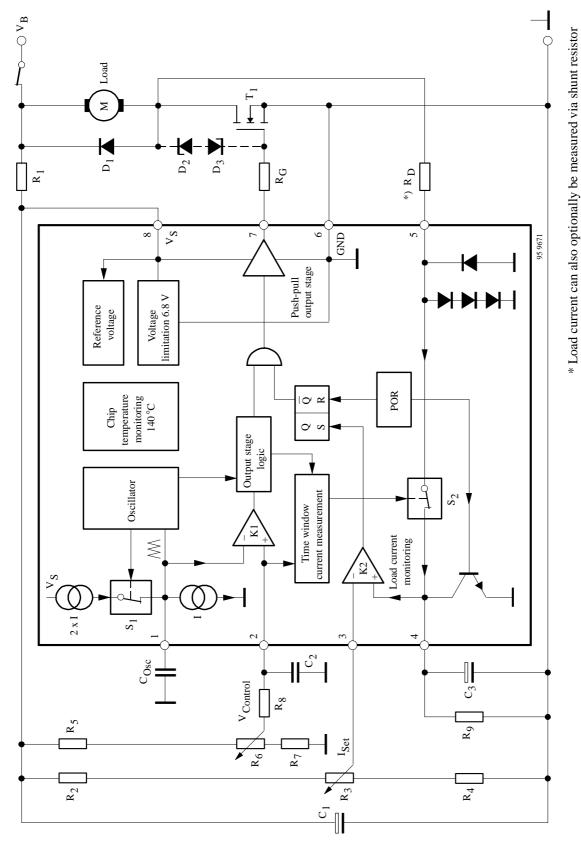

Figure 2. Block diagram with typical circuit

### **Pin Description**

## Supply, Pin 8

Internal voltage limitation in the U2352B allows a simple supply via a series resistor  $R_1$ . This enables operation of the circuit under different operating voltages. Supply voltage between Pin 8 ( $V_S$ ) and Pin 6 (GND) builds up via  $R_1$  and is smoothed by  $C_1$ .

The series resistor  $R_1$  is calculated as follows:

$$R_{1\text{max}} = \frac{V_{\text{Bmin}} - V_{\text{Smax}}}{I_{\text{tot}}}$$

where

$V_{Bmin}$  = Minimum operating voltage  $V_{Smax}$  = Maximum supply voltage

$I_{tot} = I_{Smax} + I_{X}$

$I_{Smax}$  = Maximum current consumption of the IS  $I_{X}$  = Current consumption of the external elements

Various thresholds are derived from an internal reference voltage source.

# **Voltage Monitoring**

During build-up and reduction of the operating voltage, uncontrolled output pulses with excessively low amplitude are suppressed by the internal monitoring circuit. All latches are reset and the output of the load current detection Pin 4 is switched to ground.

# **Chip Temperature Monitoring**

U2352B has integrated chip temperature monitoring which switches off the output stage when a temperature of approximately 140°C is reached. The device is not enabled again until cooling has taken place and the supply voltage has been switched off and then back on again.

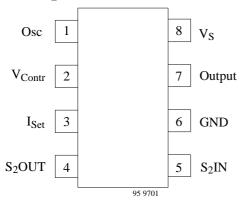

| Pin | Symbol             | Function                              |

|-----|--------------------|---------------------------------------|

| 1   | Osc                | Oscillator                            |

| 2   | V <sub>Contr</sub> | Control voltage input                 |

| 3   | $I_{Set}$          | Setpoint value current monitoring     |

| 4   | S <sub>2</sub> OUT | Output, current switch S <sub>2</sub> |

| 5   | S <sub>2</sub> IN  | Input, current switch S <sub>2</sub>  |

| 6   | GND                | Ground                                |

| 7   | Output             | Output                                |

| 8   | V <sub>S</sub>     | Supply voltage                        |

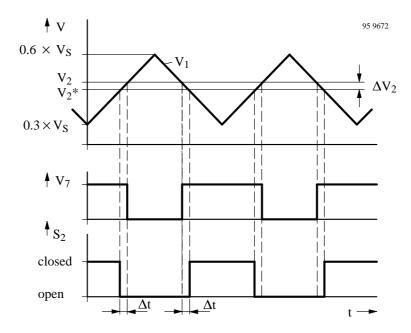

# Pulse Width Control, Pins 1 and 2

At the frequency-determining capacitor,  $C_{\rm osc}$ , at Pin 1, switching over of two internal current sources gives rise to a triangular voltage which comparator,  $K_1$ , compares with the control voltage at Pin 2. If the voltage,  $V_1$ , is more negative than the control voltage  $V_2$ , the output stage is switched on via the output stage logic. When  $C_{\rm osc}$  is charged, the whole process then runs in reverse order (see figure 3).

### Load Current Monitoring, Pins 3, 4, 5

Load current can be measured with the aid of an external shunt resistor, but this is only appropriate for decreased loads due to additional power loss and component size and costs. This involves the shunt voltage being fed directly to Pin 4 via a protective resistor (see figure 5).

In order to save component costs and additional power loss, the integrated load current monitoring allows the load current to be directly measured via the voltage drop at the on-state resistance, R<sub>DS(on)</sub>, of the FET, without an additional shunt resistor. The drain voltage of the FET is supplied via an external protective resistor to Pin 5. During the off-state of the FET, a diode clamp circuit protects the detection input, Pin 5. In the on state, the load current flowing through the FET generates a corresponding voltage drop at its  $R_{DS(on)}, \mbox{ which is in turn }$ converted into a current at Pin 5 by the protective resistor. This current reaches the integration element at Pin 4 via the switch  $S_2$ , which is only closed in the on-state of the FET. If the voltage at Pin 4 exceeds the setpoint value set at Pin 3, as a result of a high load current, the shutdown latch is set and the output stage is blocked. To enable the circuit again, it is necessary to switch the operating voltage off and then back on again.

Switch-off behavior is adjusted with the resistors at Pin 4 and Pin 5 and also with the capacitor at Pin 4.

Rev. A1, 29-May-96

A time space,  $\Delta t$ , must be observed between switching the output stage off and on and switching  $S_2$  (current measurement enable switch) in order to avoid incorrect measurement and incorrect switching-off. To create this

time window, the control voltage  $V_2$  is reduced internally about  $\Delta V_2$  = approximately 300 mV and the resulting voltage,  $V_2$ \*, is compared with the triangular voltage,  $V_1$  (see figure 3).

Figure 3. Signal characteristics of pulse width control with time window generation

## **Absolute Maximum Ratings**

Reference point Pin 6, unless otherwise specified

| Parameters                | Symbol           | Value                | Unit                |    |

|---------------------------|------------------|----------------------|---------------------|----|

| Power supply              |                  |                      |                     |    |

| current                   | Pin 8            | $I_S$                | 40                  | mA |

| $t < 10 \ \mu s$          | Pin 8            | $i_{ m S}$           | 400                 |    |

| Push-pull output stage    |                  |                      |                     |    |

| Output current            | Pin 7            | $\pm I_{O}$          | 20                  | mA |

| t < 2  ms                 | Pin 7            | ±i <sub>O</sub>      | 100                 |    |

| Input currents            | Pins 4 and 5     | $\pm I_{\mathrm{I}}$ | 10                  | mA |

| _                         | Pins 1 and 3     | $I_{\mathrm{I}}$     | 2                   |    |

| Input voltages            | Pins 1, 2 and 3  | V <sub>I</sub>       | 0 to V <sub>8</sub> | V  |

| Storage temperature range |                  | $T_{\rm stg}$        | -40 to +125         | °C |

| Junction temperature      |                  | T <sub>j</sub>       | +125                | °C |

| Ambient temperature       | T <sub>amb</sub> | -10 to +100          | °C                  |    |

### **Thermal Resistance**

| Parameters       | Symbol     | Maximum | Unit |

|------------------|------------|---------|------|

| Junction ambient |            |         |      |

| DIP8             |            | 110     |      |

| SO8 on PC board  | $R_{thJA}$ | 220     | K/W  |

| SO8 on ceramic   |            | 140     |      |

# **Electrical Characteristics**

$V_S = 6$  V,  $T_{amb} = 25$  °C, reference point Pin 6, unless otherwise specified

| Parameters                                                                                                                              | Test Condition                                                                                                                                                                                  | ns / Pins                            | Symbol                                                                       | Min.                   | Тур.                     | Max.                      | Unit                |

|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------------------------------------------------|------------------------|--------------------------|---------------------------|---------------------|

| Supply voltage limitation                                                                                                               | $I_S = 5 \text{ mA}$ $I_S = 20 \text{ mA}$                                                                                                                                                      | Pin 8                                | $V_{S}$                                                                      | 6.4<br>6.5             | 6.8<br>6.9               | 7.2<br>7.3                | V                   |

| <b>Current consumption</b>                                                                                                              | $V_S = 6 V$                                                                                                                                                                                     | Pin 8                                | Is                                                                           |                        | 2.7                      | 3.5                       | mA                  |

| Voltage monitoring                                                                                                                      |                                                                                                                                                                                                 |                                      |                                                                              |                        |                          |                           |                     |

| Switch-on threshold<br>Switch-off threshold                                                                                             |                                                                                                                                                                                                 | Pin 8<br>Pin 8                       | $egin{array}{c} V_{SON} \ V_{SOFF} \end{array}$                              | 5.2<br>4.7             | 5.6<br>5.1               | 6.0<br>5.5                | V                   |

| Oscillator $f_{OSC}$ [kHz] $\approx \frac{55}{C_{OSC}}$ [nF] $\times$ V <sub>S</sub> [V] Pin 1                                          |                                                                                                                                                                                                 |                                      |                                                                              |                        |                          |                           |                     |

| Upper threshold (0.6 × V <sub>S</sub> ) Lower threshold (0.3 × V <sub>S</sub> ) Charge current Discharge current  Control voltage input |                                                                                                                                                                                                 |                                      | $V_{Tu} \\ V_{Tl} \\ -I_{ch} \\ I_{dis}$                                     | 3.4<br>1.7<br>26<br>26 | 3.6<br>1.8<br>33<br>33   | 3.8<br>1.9<br>40<br>40    | V<br>V<br>μΑ<br>μΑ  |

| Input voltage range Input current, Offset voltage K <sub>1</sub> Window, current measurement                                            | $0 \ V \le V_2 \le V_8$                                                                                                                                                                         | Pin 2<br>Pin 2<br>Pin 2–1<br>Pin 2–1 | $\begin{array}{c} V_I \\ \pm I_i \\ \pm V_{Offs} \\ -\Delta V_2 \end{array}$ | 260                    | 300                      | V <sub>8</sub> 500 15 340 | V<br>nA<br>mV<br>mV |

| Load current monitoring                                                                                                                 | T                                                                                                                                                                                               |                                      |                                                                              |                        |                          |                           |                     |

| Setpoint value input:<br>Input voltage range<br>Input current                                                                           | $0 V \le V_3 \le 6 V$                                                                                                                                                                           | Pin 3<br>Pin 3                       | $\begin{array}{c} V_I \\ \pm I_i \end{array}$                                | 0                      |                          | 6<br>500                  | V<br>nA             |

| Offset voltage K <sub>2</sub>                                                                                                           |                                                                                                                                                                                                 | Pin 4–3                              | ±V <sub>Offs</sub>                                                           |                        |                          | 15                        | mV                  |

| Load current detection:<br>Voltage limitation<br>Voltage limitation                                                                     | $I_5 = 1 \text{ mA}$ $I_5 = -1 \text{ mA}$                                                                                                                                                      | Pin 5<br>Pin 5                       | V <sub>L</sub><br>-V <sub>L</sub>                                            |                        | 2.3<br>0.7               |                           | V                   |

| Discharge current at POR                                                                                                                |                                                                                                                                                                                                 | Pin 4                                | I <sub>dis</sub>                                                             | 1                      |                          |                           | mA                  |

| Switch S <sub>2</sub>                                                                                                                   | 1                                                                                                                                                                                               | Pin 5–4                              |                                                                              | <u> </u>               | <del>-</del>             |                           |                     |

| Residual voltage at closed switch                                                                                                       | $V_4 = 0 \text{ V},  I_5 = \\ V_4 = 0.1 \text{ V}, I_5 = \\ V_4 = 0.3 \text{ V}, I_5 = \\ V_4 = 0.3 \text{ V}, I_5 = \\ V_4 = 0.3 \text{ V}, I_5 = \\ V_4 = 0.4 \text{ V}, I_5 = 0.4 \text{ V}$ | 50 μA<br>50 μA                       | $ m V_{Sat}$                                                                 |                        | 175<br>150<br>125<br>200 |                           | mV                  |

| Push-pull output stage                                                                                                                  |                                                                                                                                                                                                 | Pin 7                                |                                                                              |                        |                          |                           |                     |

| Upper saturation voltage                                                                                                                | $I_7 = -2 \text{ mA}$                                                                                                                                                                           | Pin 7–8                              | -V <sub>Satu</sub>                                                           |                        |                          | 1                         | V                   |

| Lower saturation voltage                                                                                                                | $I_7 = 10 \text{ mA}$                                                                                                                                                                           | Pin 7                                | V <sub>Satl</sub>                                                            |                        |                          | 0.3                       | V                   |

| Output current<br>ON state<br>OFF state                                                                                                 | $t \le 2 \mu s$<br>$t \le 2 \mu s$                                                                                                                                                              |                                      | $ \begin{array}{c c} -i_0 \\ i_0 \end{array} $                               | 100<br>100             |                          |                           | mA                  |

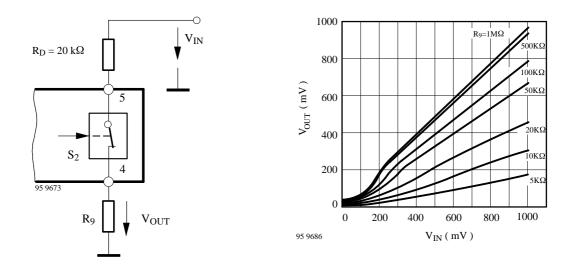

Figure 4. Typical circuitry of the current switch S2 with associated transfer characteristics (S2 closed)

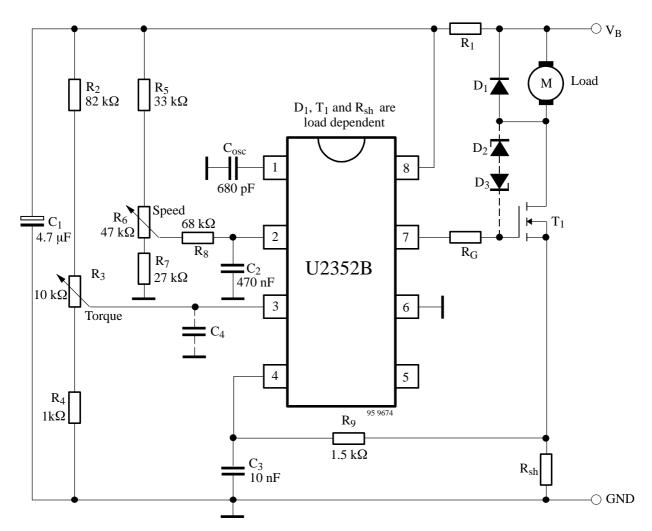

Figure 5. Speed control with load current monitoring (load current detection via shunt resistor)

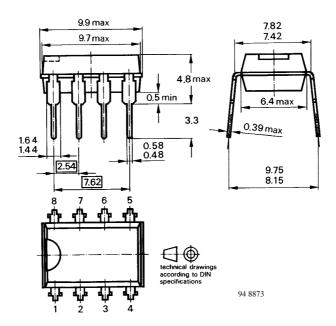

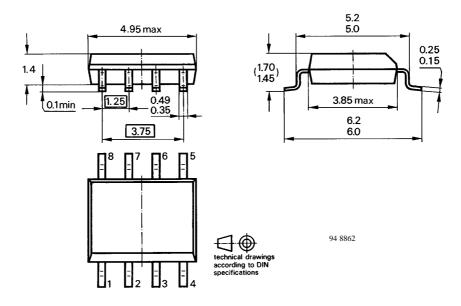

### **Dimensions in mm**

Package: DIP8

Package: SO8

### **Ozone Depleting Substances Policy Statement**

It is the policy of TEMIC TELEFUNKEN microelectronic GmbH to

- 1. Meet all present and future national and international statutory requirements.

- 2. Regularly and continuously improve the performance of our products, processes, distribution and operating systems with respect to their impact on the health and safety of our employees and the public, as well as their impact on the environment.

It is particular concern to control or eliminate releases of those substances into the atmosphere which are known as ozone depleting substances (ODSs).

The Montreal Protocol (1987) and its London Amendments (1990) intend to severely restrict the use of ODSs and forbid their use within the next ten years. Various national and international initiatives are pressing for an earlier ban on these substances.

**TEMIC TELEFUNKEN microelectronic GmbH** semiconductor division has been able to use its policy of continuous improvements to eliminate the use of ODSs listed in the following documents.

- 1. Annex A, B and list of transitional substances of the Montreal Protocol and the London Amendments respectively

- 2. Class I and II ozone depleting substances in the Clean Air Act Amendments of 1990 by the Environmental Protection Agency (EPA) in the USA

- 3. Council Decision 88/540/EEC and 91/690/EEC Annex A, B and C (transitional substances) respectively.

**TEMIC** can certify that our semiconductors are not manufactured with ozone depleting substances and do not contain such substances.

We reserve the right to make changes to improve technical design and may do so without further notice.

Parameters can vary in different applications. All operating parameters must be validated for each customer application by the customer. Should the buyer use TEMIC products for any unintended or unauthorized application, the buyer shall indemnify TEMIC against all claims, costs, damages, and expenses, arising out of, directly or indirectly, any claim of personal damage, injury or death associated with such unintended or unauthorized use.

TEMIC TELEFUNKEN microelectronic GmbH, P.O.B. 3535, D-74025 Heilbronn, Germany Telephone: 49 (0)7131 67 2831, Fax number: 49 (0)7131 67 2423